Other Parts Discussed in Thread: LMX2582

主题中讨论的其他器件:LMX2694-LMX2582、EP

工具/软件:

大家好、尊敬的 TI 支持团队

我购买了 LMX2694-LMX2694-LMX2694-LMX2694-LMX26146a EP 评估板、但我有一些问题、因此我想在此处发布它们。

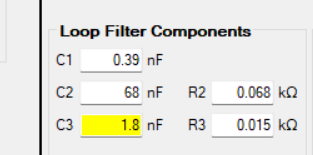

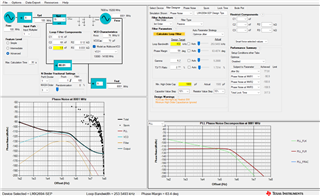

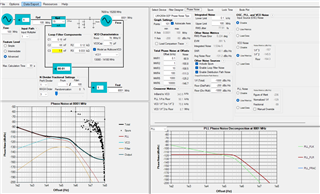

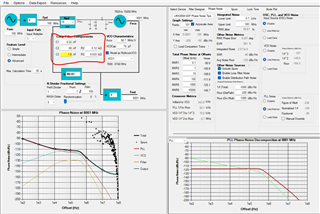

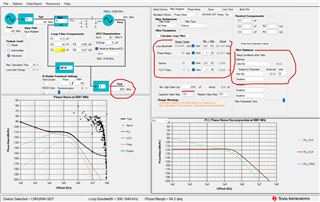

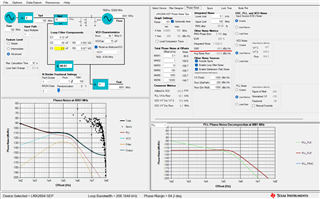

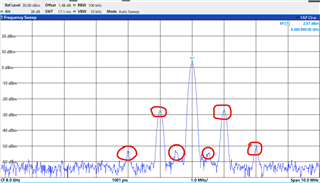

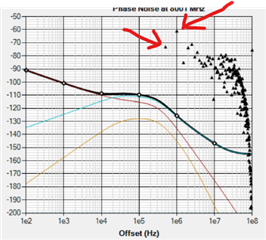

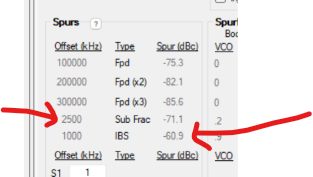

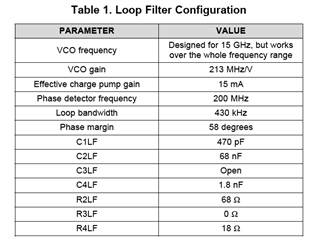

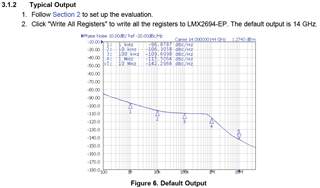

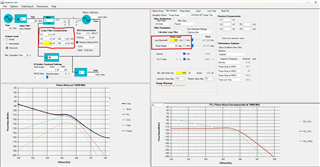

(1) 有关评估板 PDF (snau245.pdf) 图 6 中列出的结果。

我知道图 6 中的结果是根据表 1 中列出的结果得出的。 我还知道、出厂评估板上的环路滤波器常数也是表 1 中列出的值。

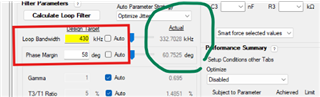

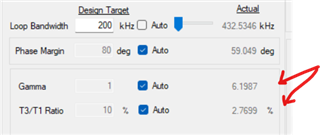

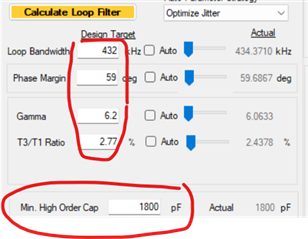

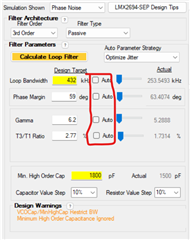

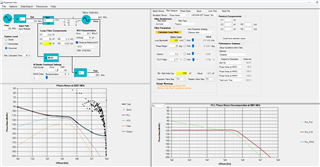

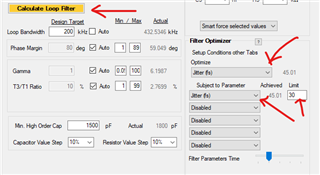

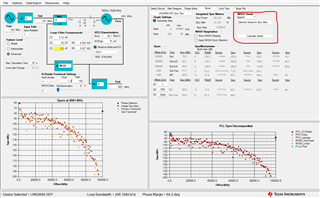

但是、当我在使用 SIM 软件 PLLatinum Sim 的相同条件下执行设计时、LoopFilter 常数会显示不同的值。

我想知道这种差异的原因以及匹配评估板结果的正确仿真方法(环路滤波器设计方法)。

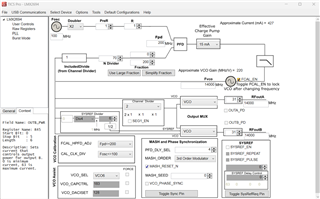

(2) 为了获得图 6、我是否应该如下图所示设置 TICS Pro?

e2e.ti.com/.../14GHzRegister.txt

请回答以上两个问题。