主题中讨论的其他器件:ADC3683、

工具/软件:

您好:

我们计划将 CDCE6214-Q1 与 ADC3683 配合使用。

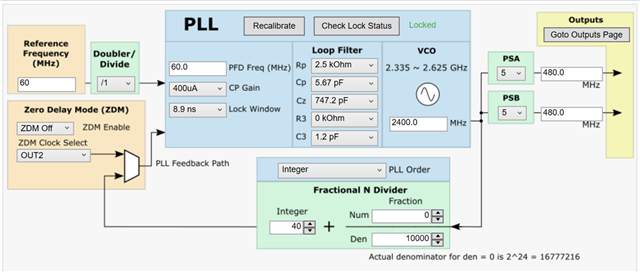

我们使用 TICSS Pro 来配置 CDCE6214-Q1 的寄存器、如下所示:

60MHz / PFD freq = 60MHz / Integer = 40 / Num = 0 且 Den = 1 / fVCO=PSA / 2400MHz = 5 的基准频率差

我们得到几个频率 OUT1 = PSA/8 = 60MHz、OUT 2 = PSA/2 = 240MHz 对应于 ADC 数据表表表 8-6 表的输出分辨率 16 位接口 2 线。

2. 60MHz / PFD freq = 60MHz / Integer = 39 / Num = 0 且 Den = 1 / fVCO=PSA / 2340MHz = 4 的基准频率差

我们得到了几个频率 OUT1 = PSA/9 = 65MHz、OUT 2 = PSA/2 = 292、5MHz 对应 ADC 默认配置输出分辨率 18 位接口 2 线(ADC 数据表表的表 8-6 中)。

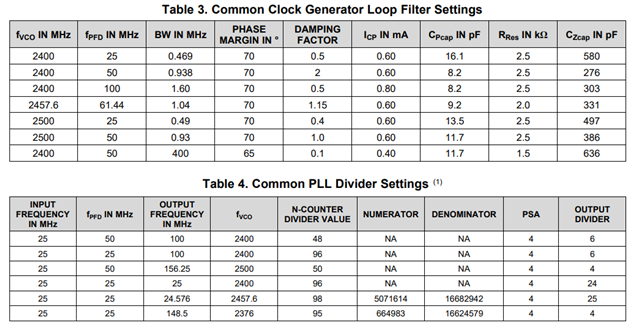

我们的问题是如何为这两个设置(CP 增益,锁定窗口和环路滤波器)正确配置 PLL 设置?

此致、