工具/软件:

尊敬的 TI 论坛:

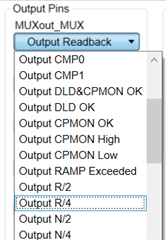

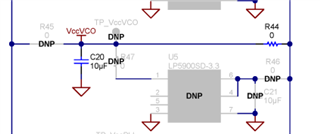

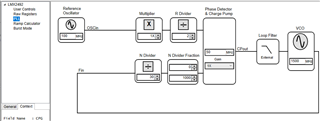

我刚才通过移除 R6 和 R4_LF、并将 RF_OUT 的 SMA 连接到 VCO RF_OUT 除以 16 (24GHz VCO 到 1.5GHz DIV)、并将 Valf 连接到 VCO 的 VTUNE、从而连接外部 VCO。 此外、我还使用 PLLatinum Sim 更改了无源滤波器的值。 在 TICS Pro 中、我配置了 PLL 选项卡、如下所示:

VCO 输出为–10dBm、但根据我在此主题中阅读的内容来看可以 (https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/742862/lmx2492-power-level-for-fin?tisearch=e2e-sitesearch&keymatch=LMX2492%25252525252520fin#)。 而 Vtune 的范围是 0V 至 1.8V

仅连接和未启用 Vtune 电压 的 VCO 的工作频率为 1.387GHz、但所需的频率为 1.5GHz、我的目标是从 1.5GHz 增加到 1.516GHz。

运行该配置时、D1 LED 不会亮起、PLL 不会生成将 VCO 频率设置为 1.5GHz 所需的 0.88V 电压。 此外、Vtune 是 0V 时的平坦信号、随机峰值为 1.8V

我想知道是否需要任何其他配置来将 PLL 配置为按预期工作。

如果需要、我可以分享更多信息。

提前感谢、

Joaquín μ s