“主题“中讨论的其他器件:、 AFE7900EVM

工具/软件:

TI 团队大家好、

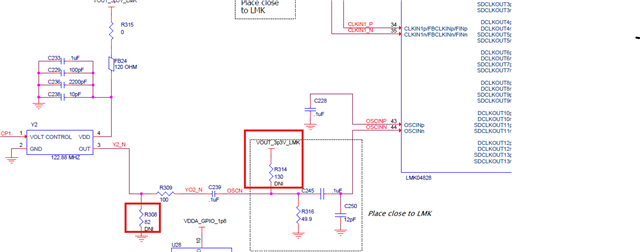

我们 在其中一个设计中使用了 LMK04828、需要了解有关振荡器输入引脚的两点。

单端时钟输入 LVCMOS 的 OSCIn 和 OSCIn 引脚上允许的最大输入电流是多少? 对于差分模式、数据表中的值为+/LVCMOS、对于–5mA、它会是多少?

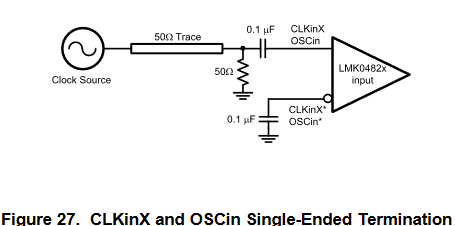

2. OSCinp 和 OSCinn 上的输入阻抗是多少?

我们使用 SiTime 振荡器、该振荡器默认在 3V3 电源下运行。在无源电路设计中、我们应使输入时钟逻辑电平处于 LMK 的可接受限制范围内、即根据数据表规定 0.2 ~ 2.4V。

对于精确的元件选择、我们希望了解上述两点。