工具/软件:

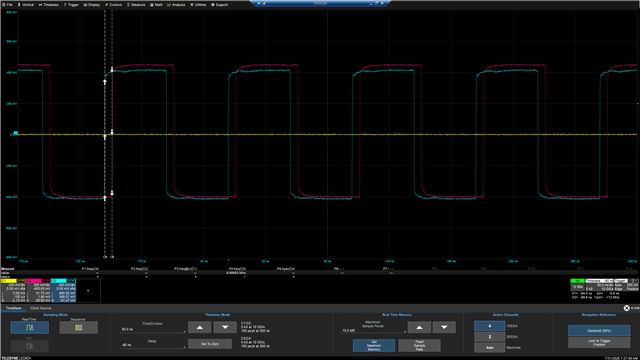

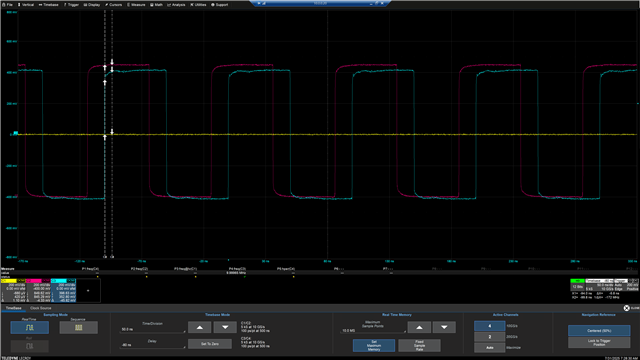

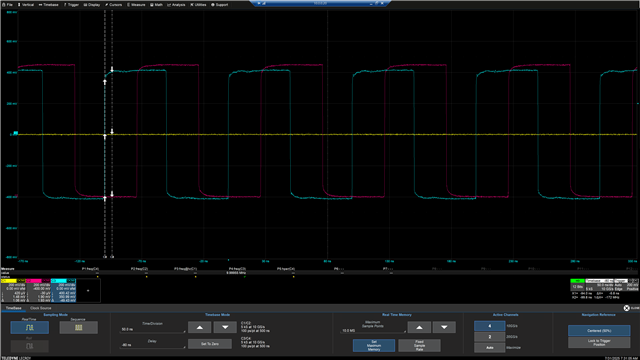

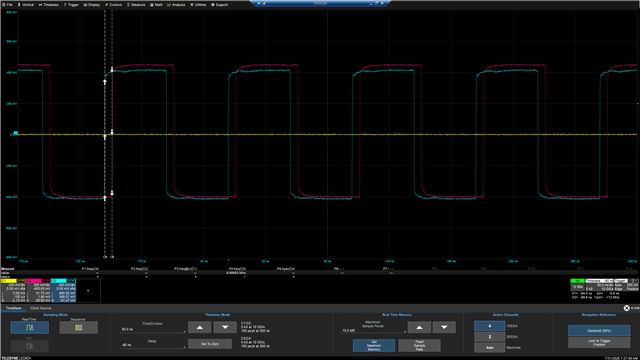

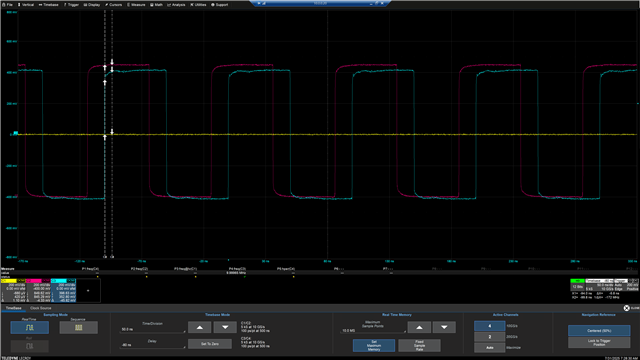

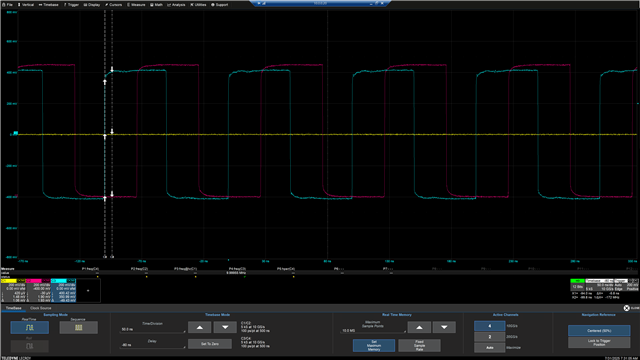

当我使用 LMK5B33414 使用 10M 基准输入测试 ZDM 模式时、我注意到复位芯片的相位存在偏差。 这可能是什么原因? 附件包含我的配置文件。 该图显示了多次复位后软件的输出通道 0 与基准时钟之间的相位差。

e2e.ti.com/.../LMK5B33414_5F00_10MHz_5F00_ZDM.rar

e2e.ti.com/.../LMK5B33414_5F00_10MHz_5F00_ZDM.rar

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

当我使用 LMK5B33414 使用 10M 基准输入测试 ZDM 模式时、我注意到复位芯片的相位存在偏差。 这可能是什么原因? 附件包含我的配置文件。 该图显示了多次复位后软件的输出通道 0 与基准时钟之间的相位差。

e2e.ti.com/.../LMK5B33414_5F00_10MHz_5F00_ZDM.rar

e2e.ti.com/.../LMK5B33414_5F00_10MHz_5F00_ZDM.rar

尊敬的 Wenhao:

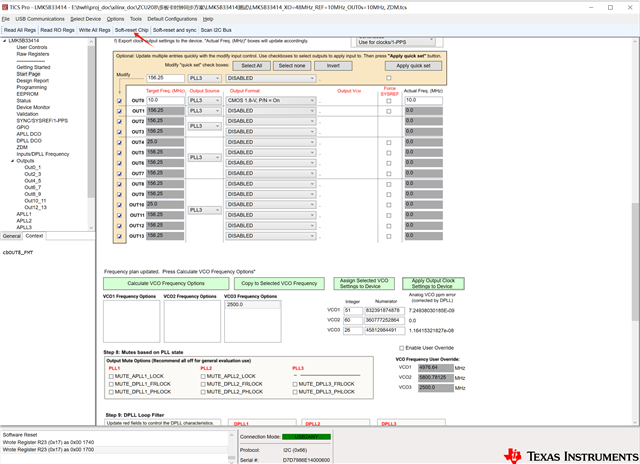

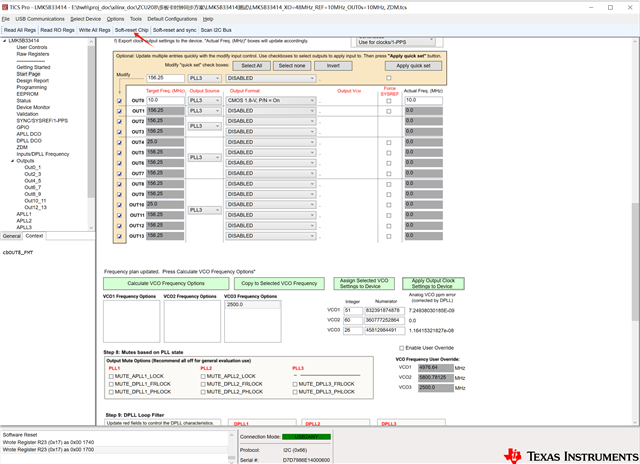

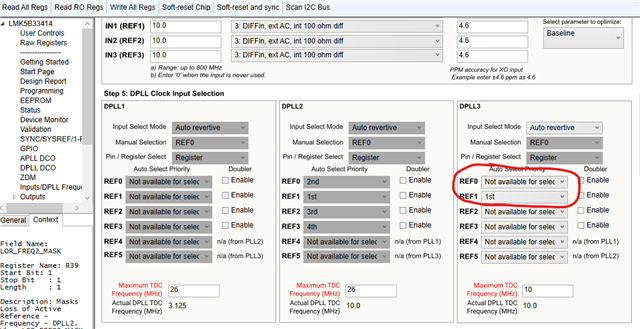

加载使用 ZDM 的 TCS 文件 DPLL3 后、配置为仅从 IN1 获取基准输入。 光学引擎的图像中。

但在参考验证框右侧的状态页面图像上、我们可以看到仅选中 REF0_VALID_STATUS。 我更改了 GUI、将 REF0 和 REF1 都作为有效的 DPLL 基准。 您是否可以尝试此新 TCS 配置并报告新状态页面以及零件是否按预期工作?

e2e.ti.com/.../LMK5B33414_5F00_10MHz TCS_5F00_ZDM-DPLL3-REF0-valid.tcs

此致、

Kyle Yamabe

您好 Wenhao、

这似乎是因为状态位尚未更新、或者在更新发生时器件锁定。

除非按下“Read Status“按钮、否则状态页面不会更新。 电路板上电后、DPLL 需要一段时间来实现相位和频率锁定。 如果在此期间点击“Read Status“按钮、我预计 LOFL_DPLL3 和 LOPL_DPLL3 在短时间内= 1。 您可以继续点击“Read Status“、并且应该看到状态位处于清除状态。

此致、

Kyle Yamabe