Other Parts Discussed in Thread: DP83869HM, LMK05318, LMK5B12212, LMK5B33414, LMK5B33216, LMK05318B, LMK05318B-Q1, AM625

Thread 中讨论的其他器件:DP83869HM、 LMK5B12212、 LMK5B33414、 LMK5B33216、 AM625、 AM6252

工具/软件:

尊敬的 TI 团队:

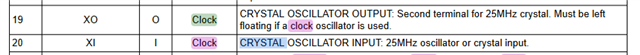

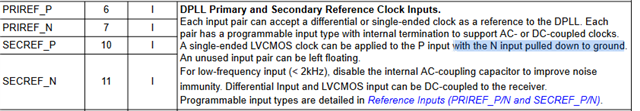

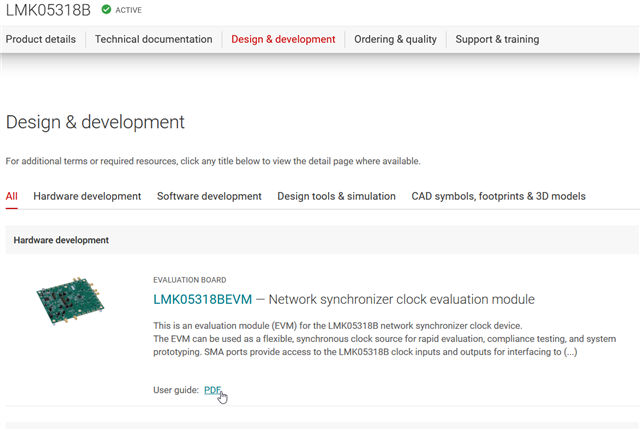

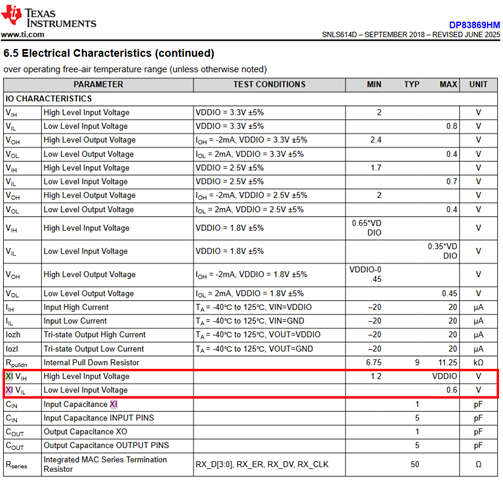

我们正在寻找连接 AM62x 配合使用 DP83869HM 用于 1Gbps 以太网连接的以太网 PHY。 此外、我们还希望为我们的系统添加 Sync E 支持、以便连接多个系统。 为此、我们 希望 使用网络同步器时钟 LMK05318。

为了实现这一目标并使设计首次成为正确的设计、我们希望在所有三个元件所需的硬件连接方面为您提供支持。 我已提及此 链接、 但无法完全清楚连接将如何进行和通信。

您能否分享 Sync E 实施系统的参考设计(如果有)?

如果不可用、请指导我们如何进行连接。

此致、

Sahil Nayak