请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK04832工具/软件:

尊敬的、TI 团队:

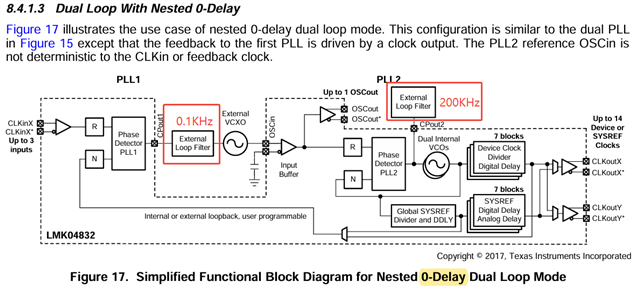

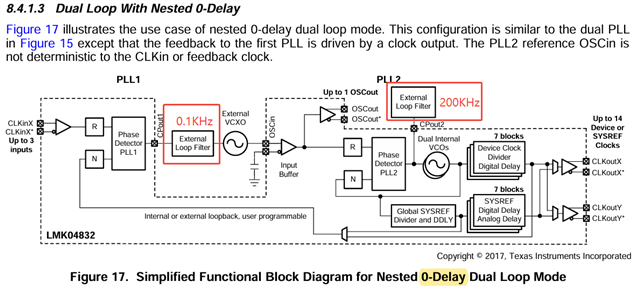

我想了解嵌套 0 延迟双环路模式下 PLL1/2 的详细锁定过程。

PLL1/2 锁定需要多长时间(环路滤波器带宽如图所示)?

在锁定过程中、芯片是否有任何输出、输出分频器是否生效?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的、TI 团队:

我想了解嵌套 0 延迟双环路模式下 PLL1/2 的详细锁定过程。

PLL1/2 锁定需要多长时间(环路滤波器带宽如图所示)?

在锁定过程中、芯片是否有任何输出、输出分频器是否生效?

谢谢!

您好、Applo、

很抱歉耽误你的时间。

PLL1/2 的锁定过程取决于相位检测器和 PLLx_DLD_CNT 的相应值。

PLLx_DLD_CNT 是用户指定的数字、用于确定在器件将锁定检测置为有效之前必须检测到锁定的周期数。

最短锁定时间可通过 PLLx_DLD_CNT/相位检测器频率计算得出。

您也可以在 Status_LD1 或 Status_LD2 引脚上输出锁定检测状态 — 这些是唯一可以指示锁定状态的输出。 即使 PLL 未锁定、输出分频器也会生效。

谢谢、

Michael