工具/软件:

尊敬的 TI 团队:

我叫 Pavan、我们目前面临着在采用 LMK04828B 的定制电路板上实现 PLL 锁定的问题。 我们已经使用 上的 19.54MHz 输入开发了一个测试应用 CLK_IN2 。 我们使用的设置 带 CLK104 模块的 ZCU208 、输入被成功锁定、然后 STATUS_LD2 指示 LMK 的输出已锁定。

不过、当在上运行相同的应用时 定制板 、LMK 未锁定、并且两者都锁定 STATUS_LD1 和 STATUS_LD2 保持低电平、指示 PLL1 和 PLL2 未锁定。

以下是设计限制和我们的观察结果:

-

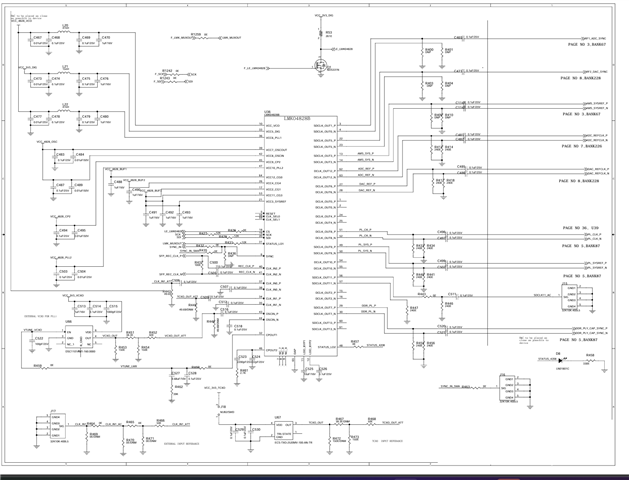

我们遵循与 CLK104 模块相同的 LMK04828B 原理图。 原始 CLK104 使用 160MHz VCXO (15PPM )、这是不可用的。 因此、我们将其替换为另一个 具有 50PPM 的 160MHz VCXO 稳定性。 所有其他原理图元件保持不变。

-

我们的定制板上、 CPOUT1 生成 1.65V 作为 VCXO 的控制电压。 不过、VCXO 需要 3.3V 控制电压 以太网端口。 为了解决这个问题、我们使用进行了测试 外部电平转换器 提升电压、但是 STATUS_LD1 和 STATUS_LD2 仍然保持低电平 — 表示 PLL 仍然未锁定。

-

我们怀疑问题可能是由引起的 VCXO 稳定性 (50PPM 与 15PPM ) 和/或 控制电压要求 。 原始 CLK104 VCXO 似乎 直接接受 1.65V。 我们还观察到 充电和放电行为 在 CPOUT1 上、表示 PLL 正在尝试调整 VCXO。 为了解决电压不兼容问题、我们计划使用 阈值为 1.65V 的比较器 VCXO。

-

我们考虑将 VCXO 替换为 A 较低的 PPM(例如<10PPM) 相同频率版本、以便匹配原始 CLK104 设计的性能。

我们还上传了定制原理图以及 CLK104 LMK 原理图以供参考。

请建议适当的解决方案或建议、以帮助解决此问题。

此致、

Pavan