您好、

我们在其中一个项目中使用了 CDCI6214RGE。

我们使用 Y0 输出 LVCMOS 时钟。

我们还使用 Y2 和 Y3 来生成 LVDS 时钟。 (100MHz 和 125MHz)。

输入时钟来自连接到 XIN 和 XOUT 的 25MHz 晶体。

Y2 和 Y3 处的时钟会按预期工作。

如果我仅输出 25MHz 且 IP_BYP_MUX 设置为 0h(为 Y0 选择 REF)、则 Y0 有效。

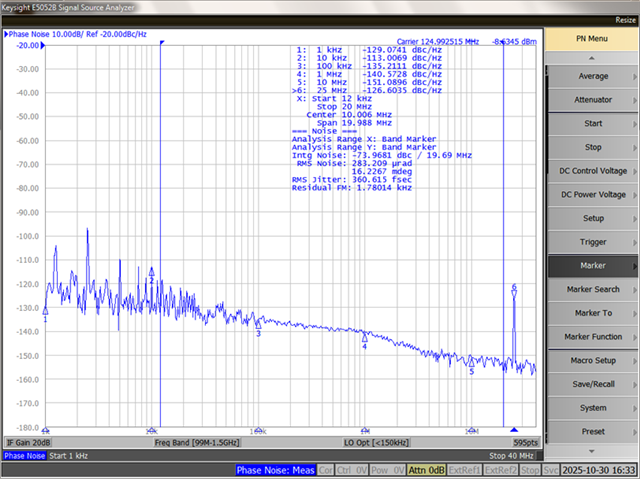

请参见下图:

如果我将 IP_BYP_MUX 设置为 1h(为 Y0 选择 PFD)并启用倍频器 (IP_rdiv = 0h) 以在 Y0 处获得 50MHz、则 Y0 处的时钟不可用、如下所示:

有什么想法什么可能是问题? Y0 是否限制为特定频率? 倍频器如何影响 Y2 和 Y3 处的 PLL 和 LVDS 时钟(抖动等)?

谢谢、此致、

Patrick