Other Parts Discussed in Thread: LMX2820

器件型号: LMX2820EVM

主题: LMX2820 中讨论的其他器件

工具/软件:

您好的团队、

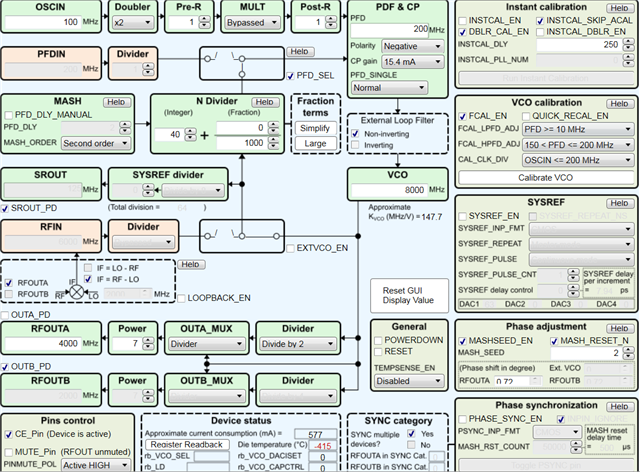

我使用 PLL LMX2820 的评估板生成高达 4GHz 的输出频率。

基准输入是来自低噪声振荡器的 100MHz 正弦波、 输出功率约为+9dBm。

下图显示了 LMX2820 配置:

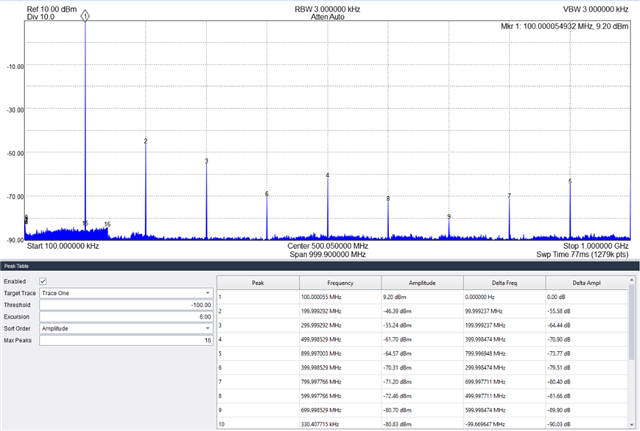

我尝试用 3 个具有不同谐波电平的基准时钟测量 PLL 输出端 4GHz 的相位噪声。

设置 1

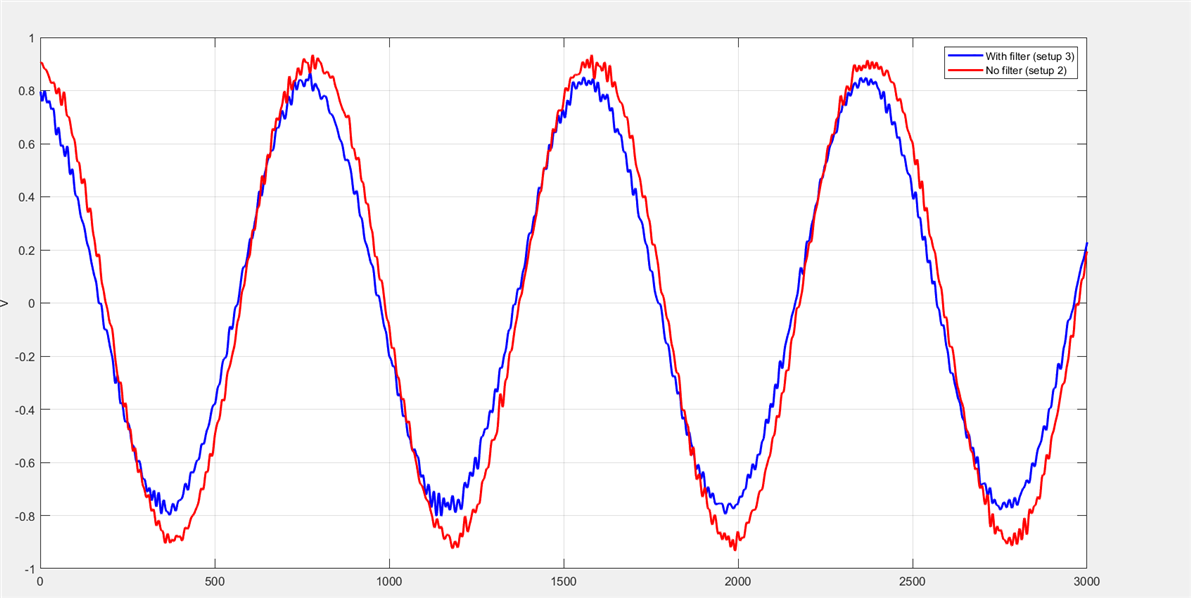

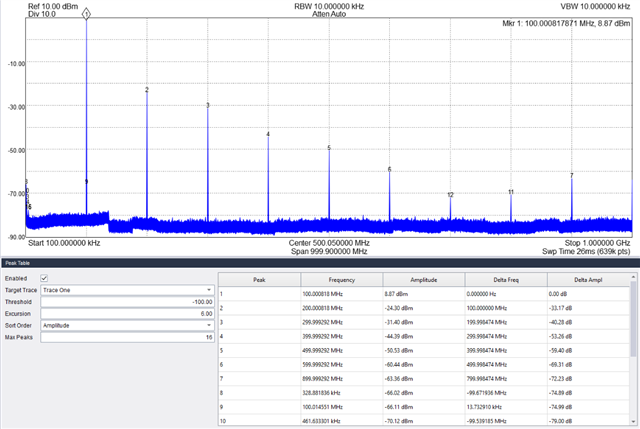

基准时钟如下图所示:

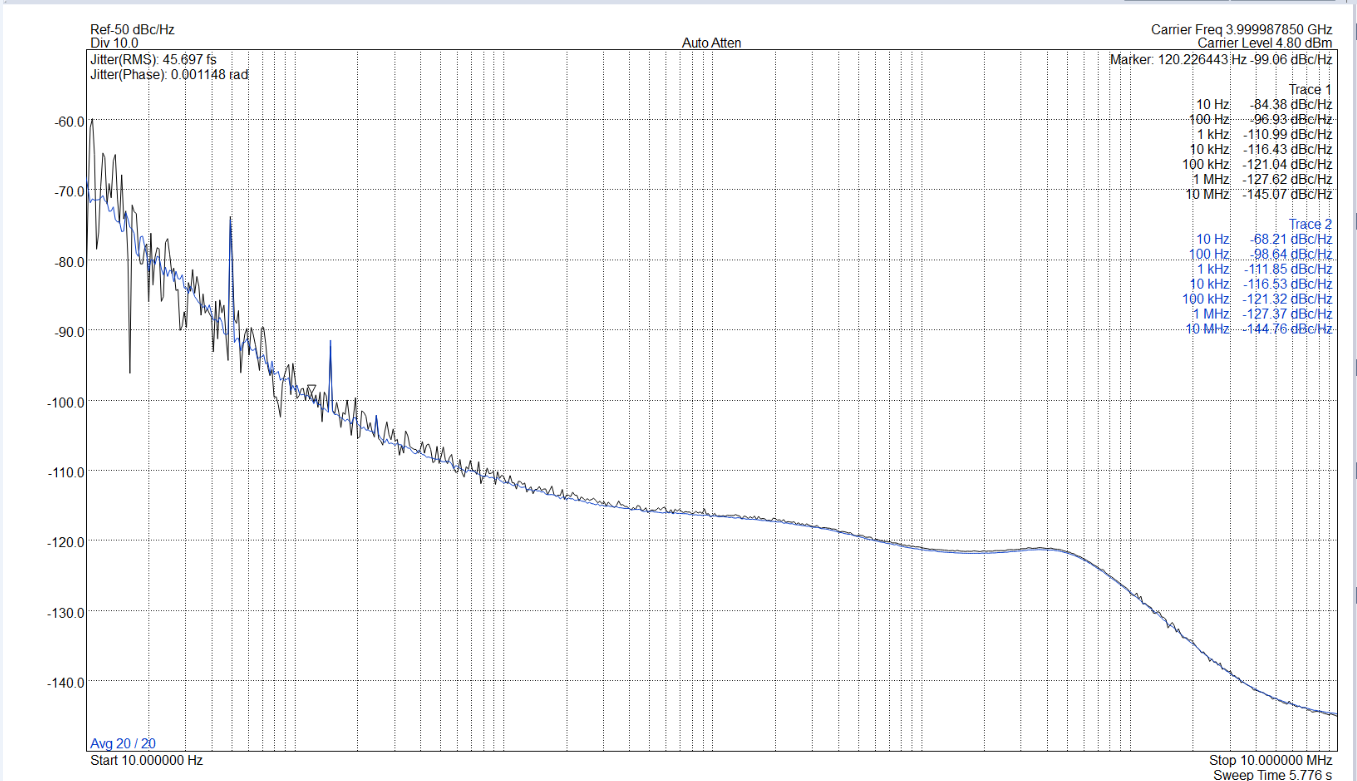

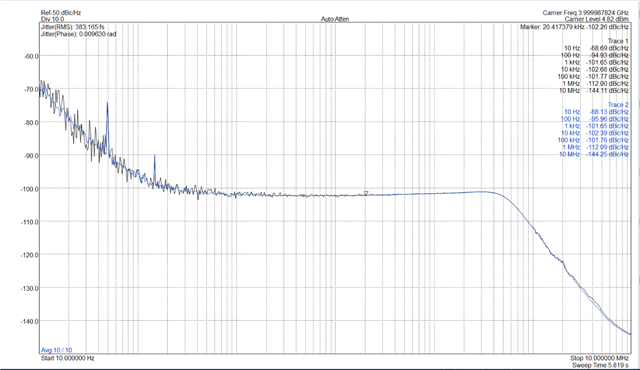

下图展示了 PLL 输出端 4GHz 时的相位噪声:

相位噪声正常

设置 2.

基准时钟如下图所示:

下图展示了 PLL 输出端 4GHz 时的相位噪声:

相位噪声不正常

设置 3.

我插入了 2 个低通滤波器 以消除基准时钟的谐波。

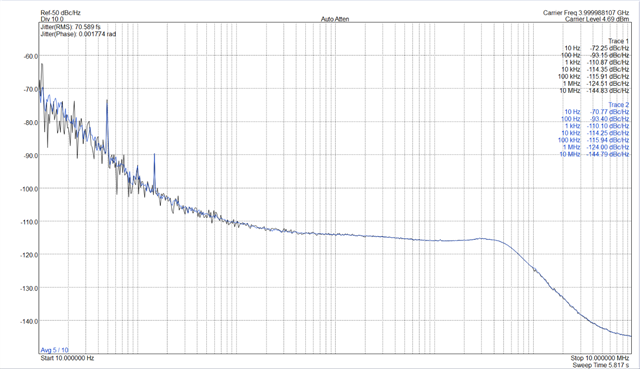

下图展示了 PLL 输出端 4GHz 时的相位噪声:

相位噪声正常

因此、全部 3 种设置的压摆率相同、但谐波电平不同。

为什么设置 2 的基准时钟的频谱含量会对相位噪声产生负面影响?

提前感谢您。

此致、

Matteo Ricci