请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号: LMK5C22212A

尊敬的团队:

我们计划使用以下器件进行时钟分配。 请澄清以下几点:

-

我们打算仅将 OCXO (CMOS 49MHz) 信号连接到振荡器输入 (XO)、同时使 CLKIN0_P/N 和 CLKIN1_P/N 保持未连接状态。 此配置是否会允许器件在 APLL 模式下运行并仍生成所有需要的输出时钟?

-

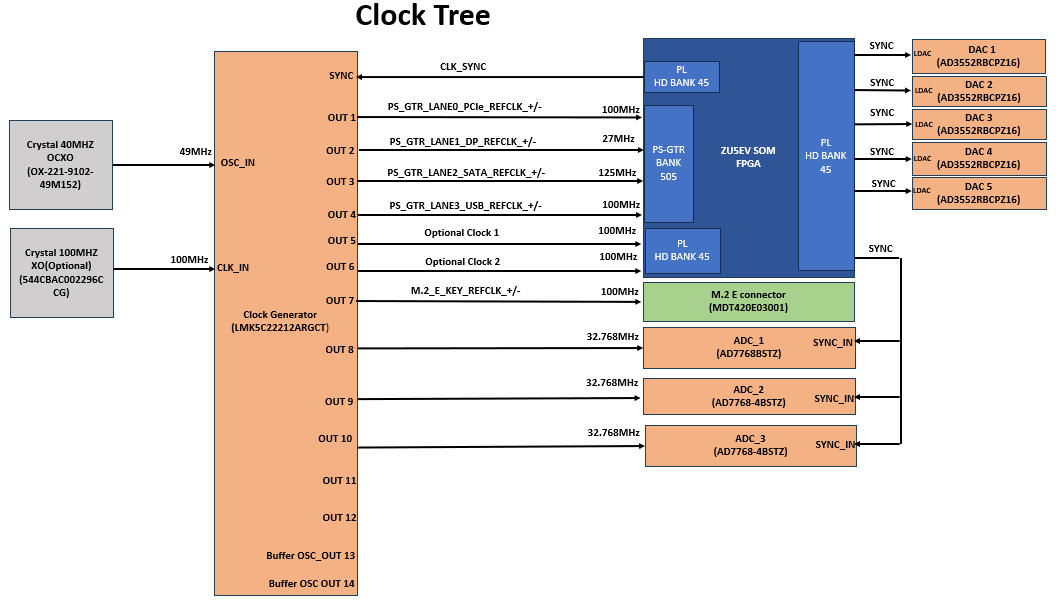

附加了审核所需的时钟树。

此致、

Vinay