器件型号: LMK04808

您好、

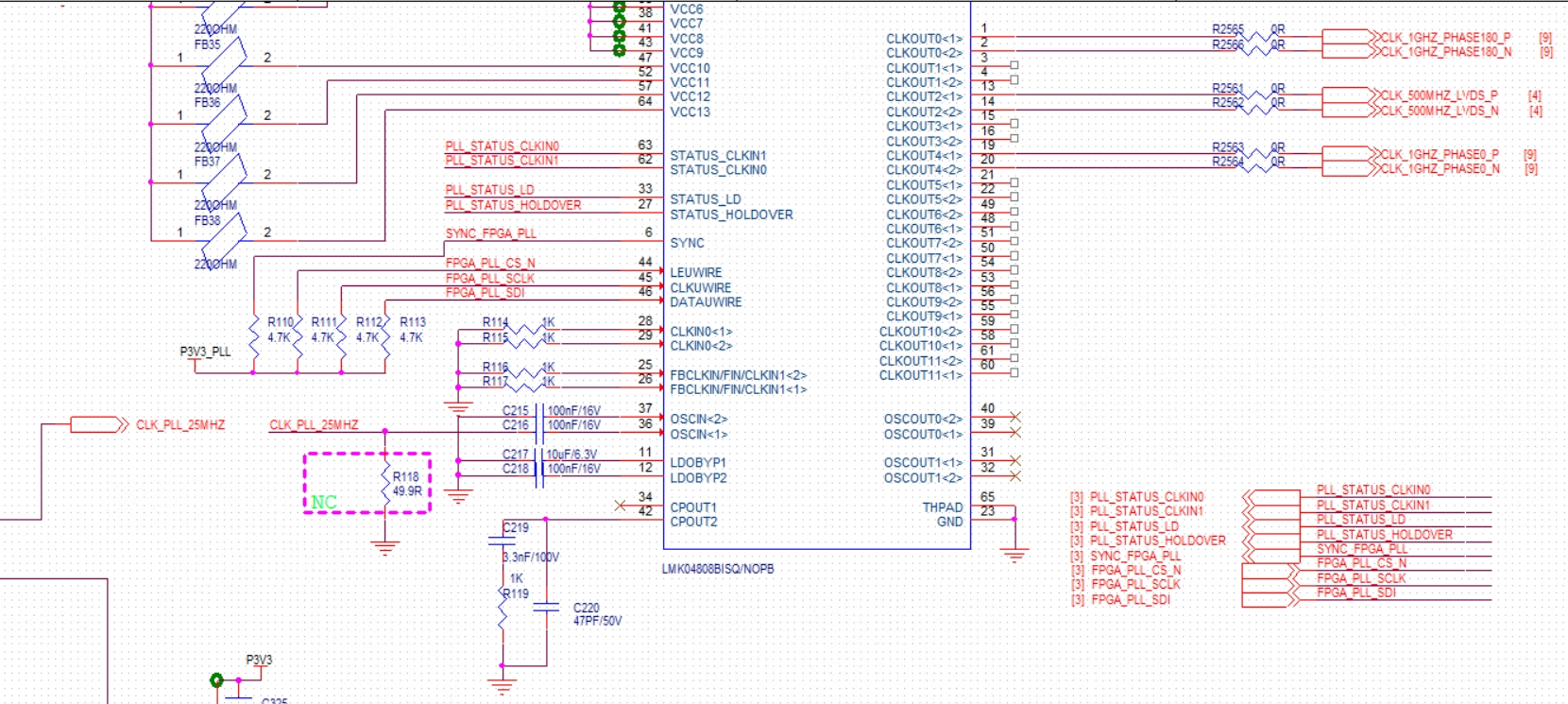

我们正在使用 LMK04808B 生成 1G 和 500m、配置输出时钟为 1.07G 后、您能帮助查看我们的寄存器和环过滤器 2 值吗? 我尝试了另一个环 filter2:(C1=15pF、C2=6.8nF、R2=560 Ω)、没有区别、这里是我们的配置和原理图。

R0 (INIT) 0x80160140

R0 0x00140060

R1 0x801400C1

R2 0x80140062

R3 0x80140043

R4 0x80140144

R5 0x80140145

R6 0x01010006

R7 0x01010007

R8 0x04010008

R9 0x5555549

R10 0x9102410A

R11 0x3401102B

R12 0x1B0C006C

R13 0x2302820D

R14 0x0200000E

R15 0x8000800F

R16 0xC1550410

R24 0x00000058

R25 0x02C9C419

0xAR26 FA8001A

R27 0x1000051B

R28 0x0010051C

R29 0x0080051D

R30 0x010003DE

R31 0x001F001F

谢谢

Bruce