Other Parts Discussed in Thread: CDCEL937, CDCEL949, CDCEL925, LMK03318, CDCE925, LMK5B12204

部件号: CDCEL925

Thread 中讨论的其他器件: LMK03318、 CDCE925、CDCEL937 、CDCEL949、 LMK5B12204

您好、

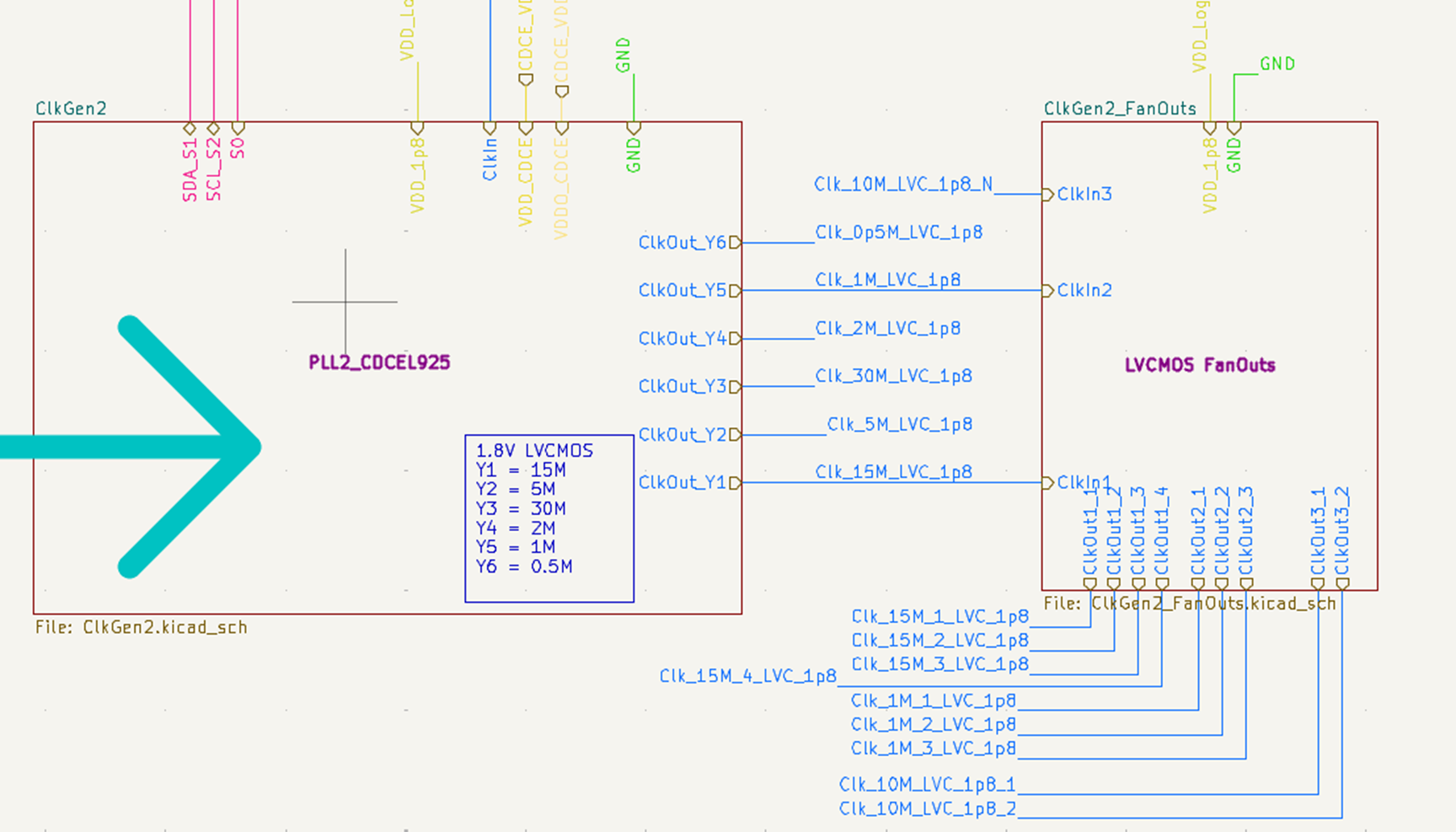

我已经使用这个 PLL 创建了一个时钟树。 我使用快速与非门创建 25%占空比的波形。 原理图如下所示:

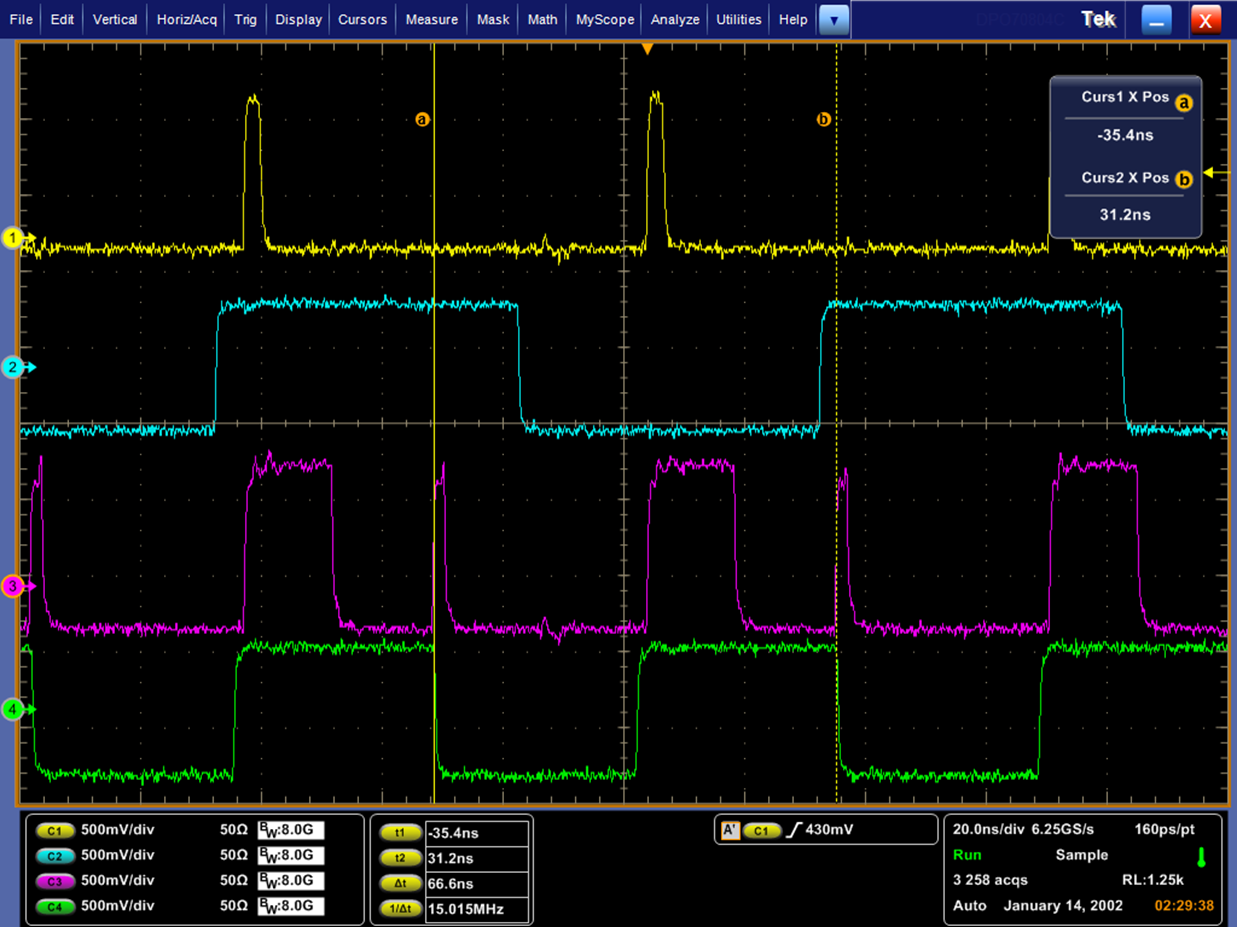

但是、当我在示波器上测量它们时、我会看到以下额外尖峰:

上面的品红色曲线是来自 PLL 的 30MHz 和 15MHz 时钟的与运算结果。 当 I 和来自 PLL 的 2M 时钟和 1M 时钟时、我会看到类似的尖峰。

进行 PCB 布线的布线长度分析时、计算出馈入与门的最大偏移为 0.1ns。 不用说、我的设计中没有考虑到传播延迟。 TI 是否有可用于此目的的软件工具? 特别是、我可以安全地假设输出组的相位同步小于 0.1ns 吗? 如果没有、我的时钟源应该追溯到 VCO 吗?

我还需要指出的是、我正在使用 LMK03318 作为基础 PLL、该 PLL 将 10MHz LVCMOS 输入驱动到 CDCEL925 中。 LMK03318 的其他组正在驱动 LVPECL 时钟、我使用这些 LVPECL 时钟做了类似的事情。 满足我的预期。

谢谢、

Prasoon