“线程”中讨论的其他部件: LMK04832, LMK04610, LMK03318, 测试

您好,

首先是一些背景:

我将您 的 LMK04832EVM 板与 KeySight DSO404A 示波器连接。 我在所选的 CLKout 上看到一个输出,但从 GUI 上选择的频率(TIC Pro)和示波器上观察到的频率(约30MHz)有偏移。

当我将 VCO_MUX 切换为 CLKin1并提供外部时钟时, 主板 会观察时钟缓冲器(可能是其划分的外部信号频率),而不是我要查看的 CLKout 上的选定频率。

此外,我还需要有关设置外部同步时钟的帮助。 我使用的外部参考时钟频率为122.88MHz。 PLL2的 LED 指示灯亮起表示锁定,但 PLL1的 LED 指示灯未亮起,我不确定这是什么原因,或者这是否表明存在问题。

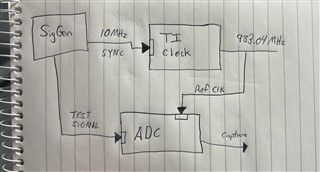

我要实现的目标:

我的目标是在使用外部同步时,有两个 CLKout,一个为980MHz,一个为10MHz。

如果您可以分享关于如何实现此设置的 TIC Pro GUI 屏幕截图,这将非常有用。

此致,

亚历克斯