你(们)好

如果我们问 LMK05318B,您会介意吗?

我们附上.TCS 文件

e2e.ti.com/.../20220113_5F00_REF_2D00_54M053998_5F005F00_OUT7_2D00_54M053998_5F005F00_220113.tcs

如果在设置的 DPLL 上运行运行脚本,则会显示错误消息。

警告:输入的值大于最大连续色调。

(在我们的操作系统中,它是用日语显示的,因此咒语可能 不正确。)

您能否告诉我们如何修改?

此致,

松本宏

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好

如果我们问 LMK05318B,您会介意吗?

我们附上.TCS 文件

e2e.ti.com/.../20220113_5F00_REF_2D00_54M053998_5F005F00_OUT7_2D00_54M053998_5F005F00_220113.tcs

如果在设置的 DPLL 上运行运行脚本,则会显示错误消息。

警告:输入的值大于最大连续色调。

(在我们的操作系统中,它是用日语显示的,因此咒语可能 不正确。)

您能否告诉我们如何修改?

此致,

松本宏

松本山,您好!

基本上,这意味着 DPLL 计算中使用的浮点数超过浮点数的最大连续范围。 由于分子和分母最终被强制调整到 DPLL 分子/分母寄存器的2^40位范围内,因此实际上可以避免任何非连续浮子问题。 我已经检查了输出并修改了内部变量以防止出现此问题,并且寄存器输出文件是相同的。

如果您仍想彻底消除此问题:

此致,

德里克·佩恩

德里克·桑

非常感谢您的回复。

好的,我们明白了。

我们还有其他问题。

在 20220113_REF-54M053998__OUT7-54M053998__220113.TCS 文件上,

OUTPUT7频率显示为54.054MHz。

在使用 VCO 和分禾器的计算中,

VCO:5675.6698MHz

-PLL2分线器: 5.

-OUTPUT7分禾器:21.

5675.6698MHz÷5 ÷21 = 54.0539980952381MHz

但是,TISPRO 显示54.054MHz。

实际输出频率是否为 54.0539980952381MHz?

此致,

松本宏

松本-桑,

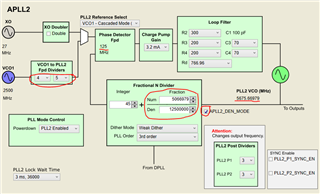

是的,输出将出现轻微 PPB 错误,PLL2上的默认分母为。 纠正这种情况的一种方法是使用手动 DCO,但这需要循环来纠正错误。 如果我们要确保按设计存在零 PPB 错误,我们可以使用 APL2_DEN_MODE 位手动修改 PLL2配置,并更改层叠参考分隔线:

54.053998MHz * 5 * 21 = 5675.66979MHz

2500MHz/20=125MHz

5675.66979MHz / 125MHz = 45 + 5_066_979 / 12_500_000 (可读性的下划线)

我们将在 Advanced (高级)-> APLL2页面上进行以下更改:

此致,

德里克·佩恩