请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:LMK0.4828万 您好,

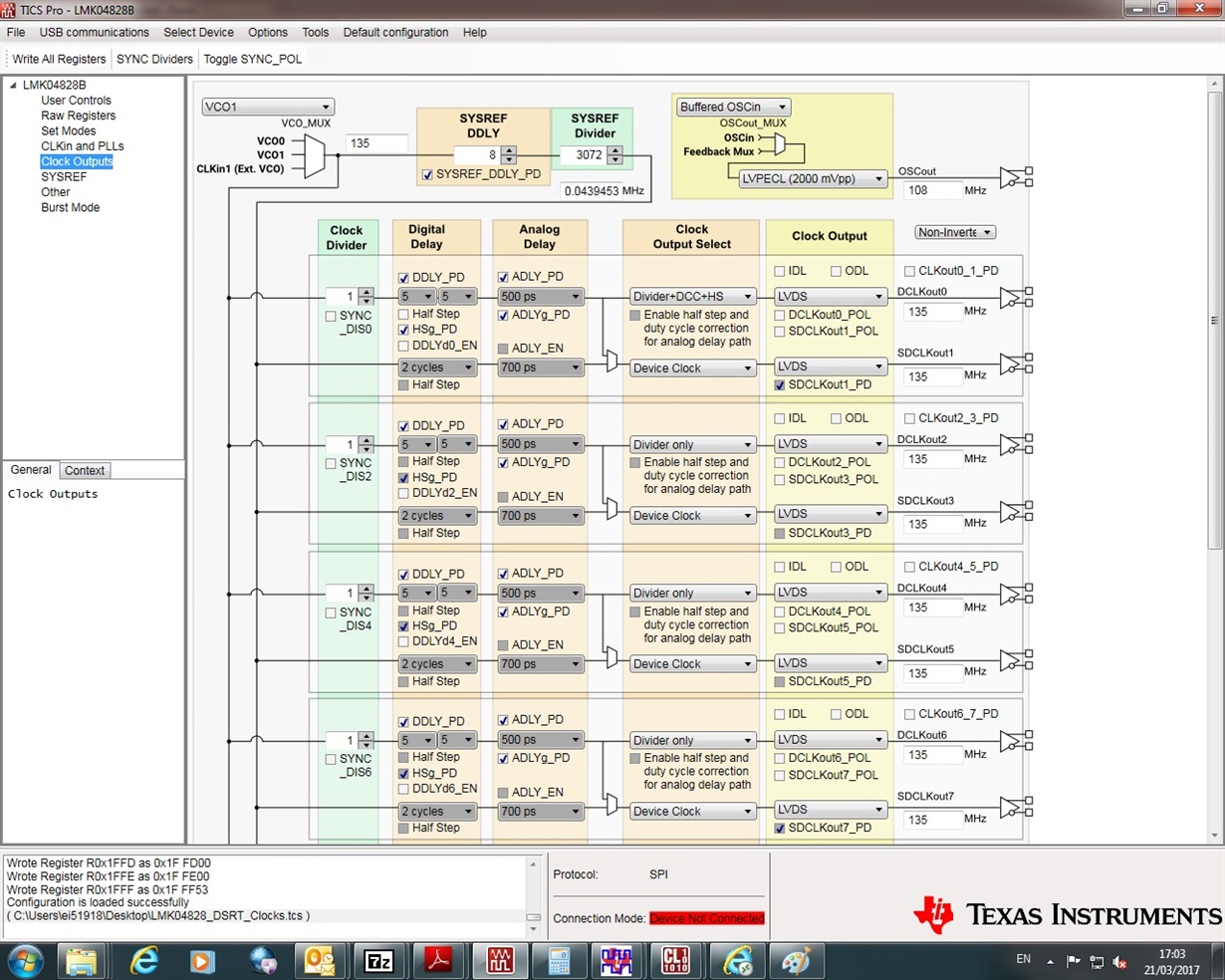

我想将LMK0.4828万用作 我的卡中所有JESD204B时钟和sysref的PLL和时钟驱动程序。

LMK0.4828万将获得108M的OSCin输入引脚, 并且仅使用PLL2时,该设备将驱动135M时钟和sysref。

我不会使用外部VCXO。 PLL1将被禁用。

我使用TIC软件设计系统。

请告诉我所附的TIC设计是否正常?

谢谢!