我尝试将两个从属LMK与主LMK同步,提供156MHz参考和同步。

主LMK :SYNC_MODE = SYNC PIN;SYSREF MUX =正常同步

SYNC_DISSYSREF位在主LMK输出同步后启用,因此主同步PIN操作将通过CLKIN0 PIN触发从LMK

从属LMK:SYNC_MODE=SYNC PIN已禁用;CLKin0_OUTPT_MUX = SYSREF_MUX;SYSREF MUX =正常同步;

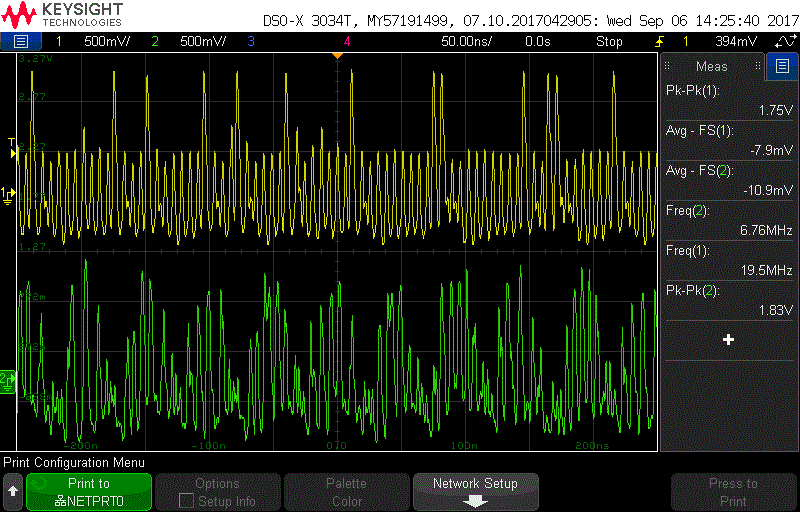

当Mater LMK SYNC PIN =0时,从属DCL为 混乱波形,

所以CLKIN0路径上一定有一些东西,示波器在从属LMK的CLKIN0 PIN上会有一些20mVpp的噪音,不应该是一个问题。

但是从LMK的SDCLK输出不是静态逻辑低电平

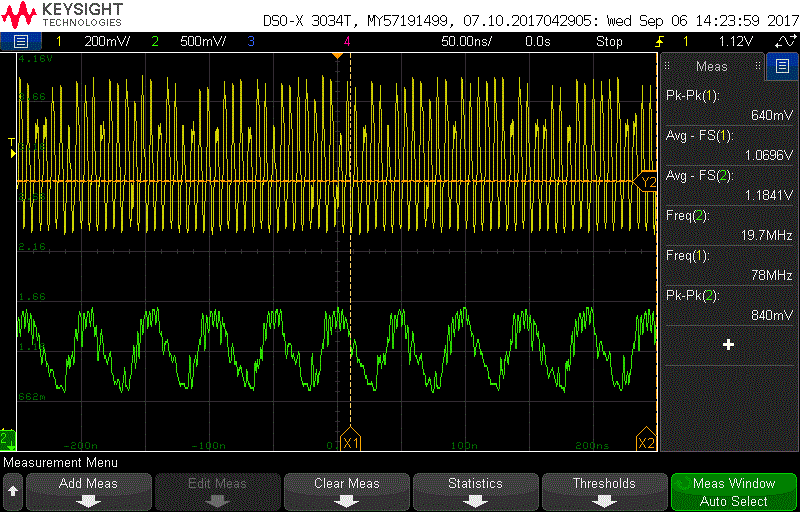

如果我设置从属LMK reg 0x0144=0xFF,DCLK输出波形将恢复正常,但两个LMK未同步。

我还尝试用SYNC_PIN模式测试从LMK芯片,SDCLK输出是SYNC PIN逻辑的对应,DCLK输出是预期的,所以芯片很好。

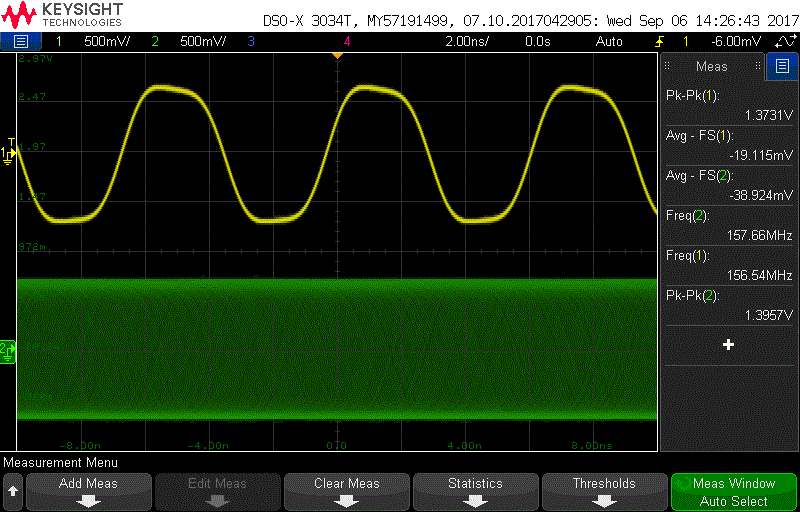

主LMK至从LMK CLKIN0的SDCLK输出为100欧姆差分,100欧姆匹配电阻,后跟0.1UF电流。主SDCLK输出为LVDS或HSDS。

主SDCLK输出到从属CLKIN0路径中肯定有问题,可能是什么问题?