大家好,团队:

我正在帮助客户使用LVDS输出格式模拟SDCLKout波形的SI,以获得122.88MHz的信号输出。

我已经做了两次测试:

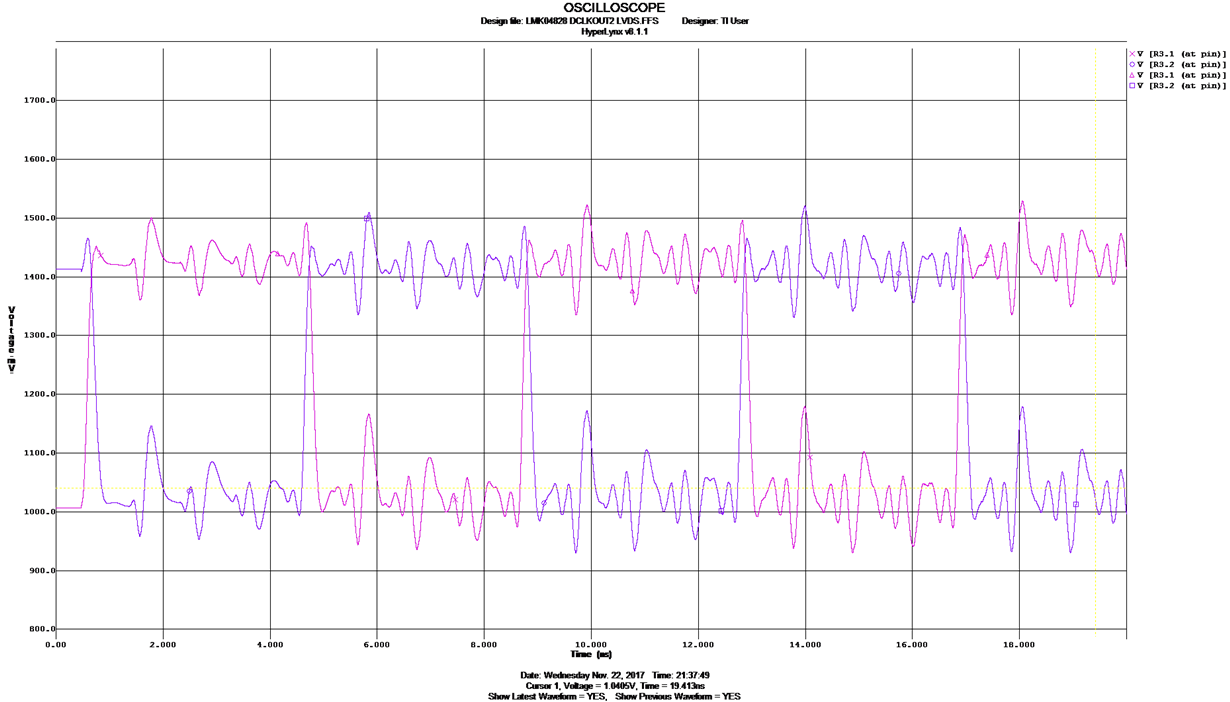

首先,我在LMK0.4828万 SDCLKout输出和区分100欧姆端接之间连接100nF交流耦合盖。 我发现100欧姆负载电阻两端的波形接线如下:

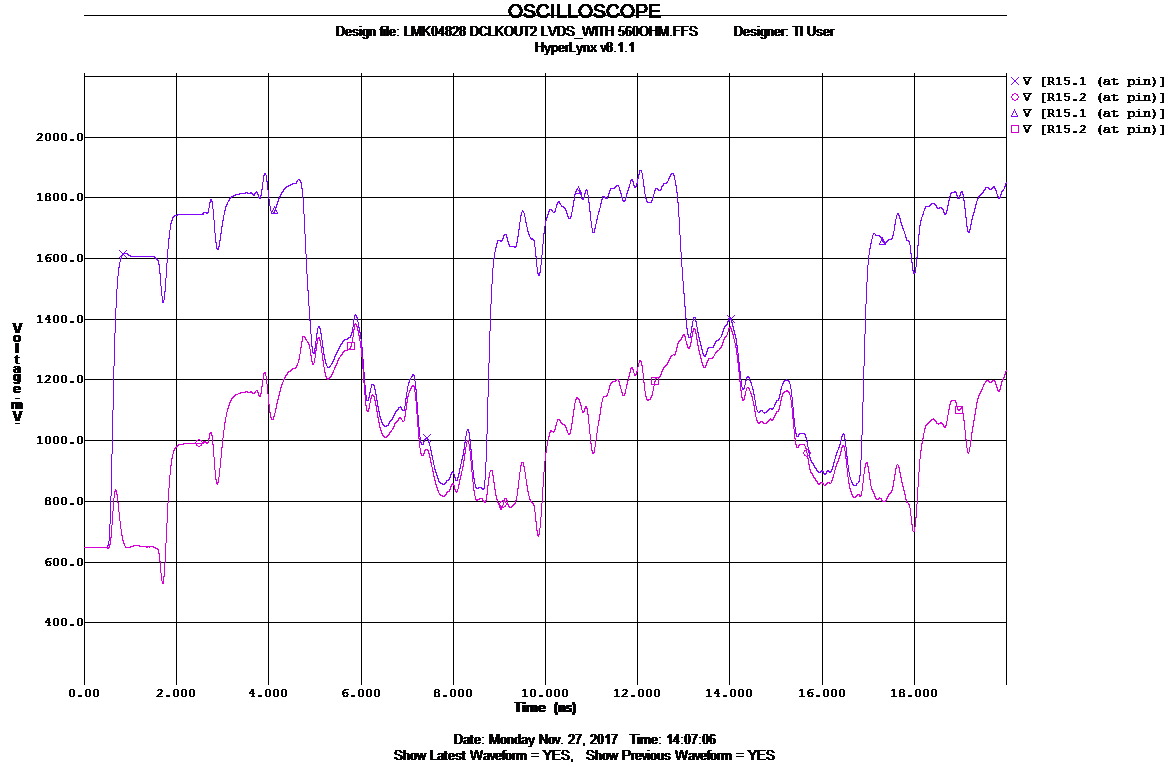

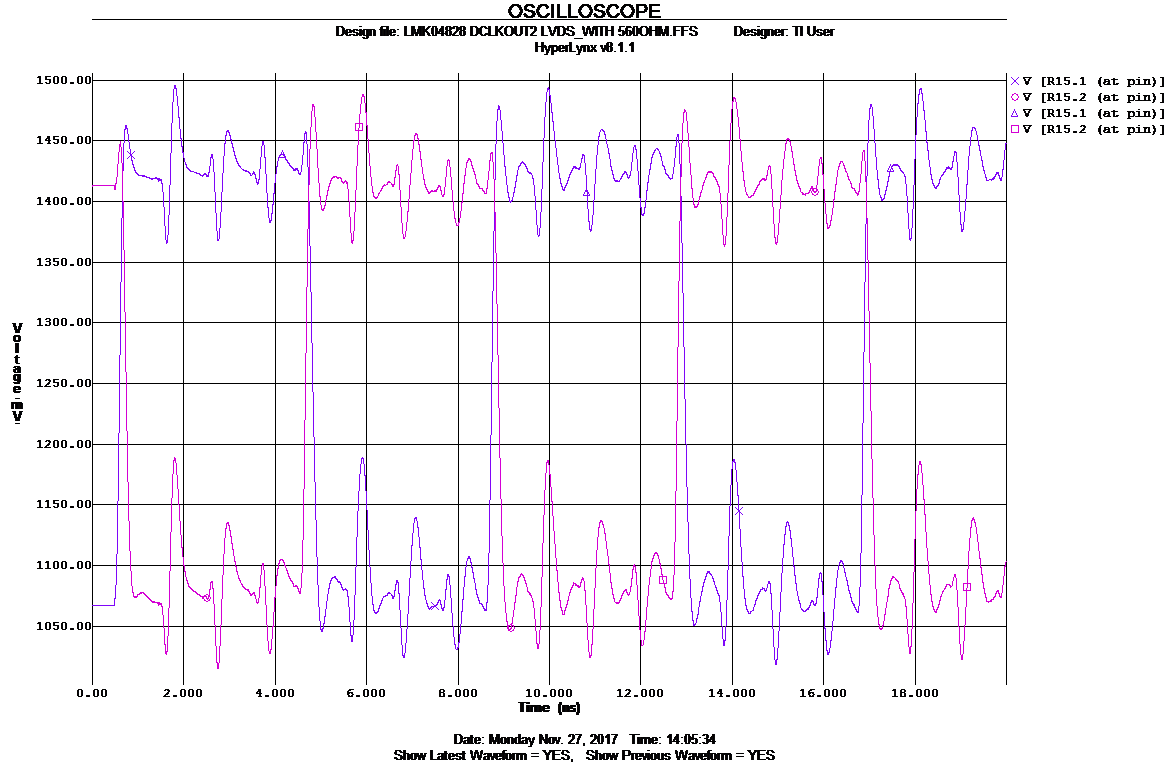

2.第二次,我取下交流耦合器帽,然后再次进行分离。 我发现波形更合理,其共模为1.2V,同时显示大量振铃。 您认为这是正确的吗?

请问为什么需要取下传输器和负载之间的交流耦合盖? 请您帮助我检查我第二次测试中的模拟是否正确吗? 我不知道为什么会有很多响铃。

我的Hyperlynx模拟文件如下所示: