专家,您好:

客户计划在缓冲模式下使用LMK0.4828万,而不是PLL2锁定模式,以便为数据转换器分配245.76MHz器件时钟,以进行同步采样。

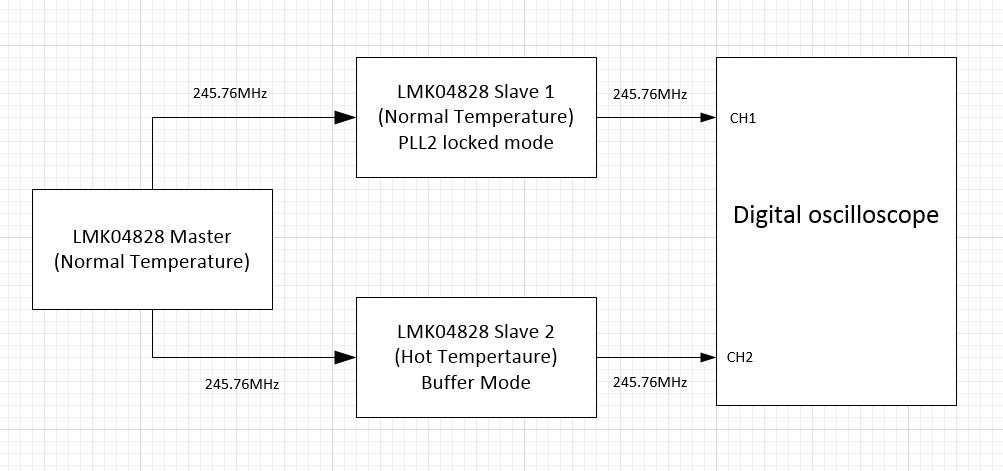

结构图如下所示:

我们将LMK0.4828万从机1置于PLL2仅模式下工作,该模式锁定到2457.6MHz的VCO频率。

将LMK0.4828万从机2置于缓冲模式下工作,该模式接受来自CLKin1的245.76MHz,并将其直接通过CLKin1_UT_MUX和VCO_MUX缓冲到DCLKout,如下所示。 DDLY,模拟DLY,DCC都被禁用,除法器也在时钟缓冲模式下被绕过。

- 为了验证相位漂移性能,我们只加热LMK0.4828万从属设备2,并将其环境温度提高15度。 然后我们发现当从属设备2的环境温度变化时,在范围变化~100 ps时观察到的时钟相位差异。 (一个时钟周期为~4ns)

- 当我们将这两个从LMK0.4828万置于PLL2锁定模式时,只有加热LMK0.4828万从2不会得到这两个LMK0.4828万之间的相位差变化过大。

我们正在考虑在时钟分配模式下工作,将使我们在温度范围内获得更稳定的相位漂移性能,而我们的测试结果显示不同的方向。 您能否帮助我们检查我们的设置中可能存在的错误? 或者我们是否有类似的LMK0.4828万相位漂移数据? 提前感谢您的帮助。

纱线