请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:LMX2594 大家好

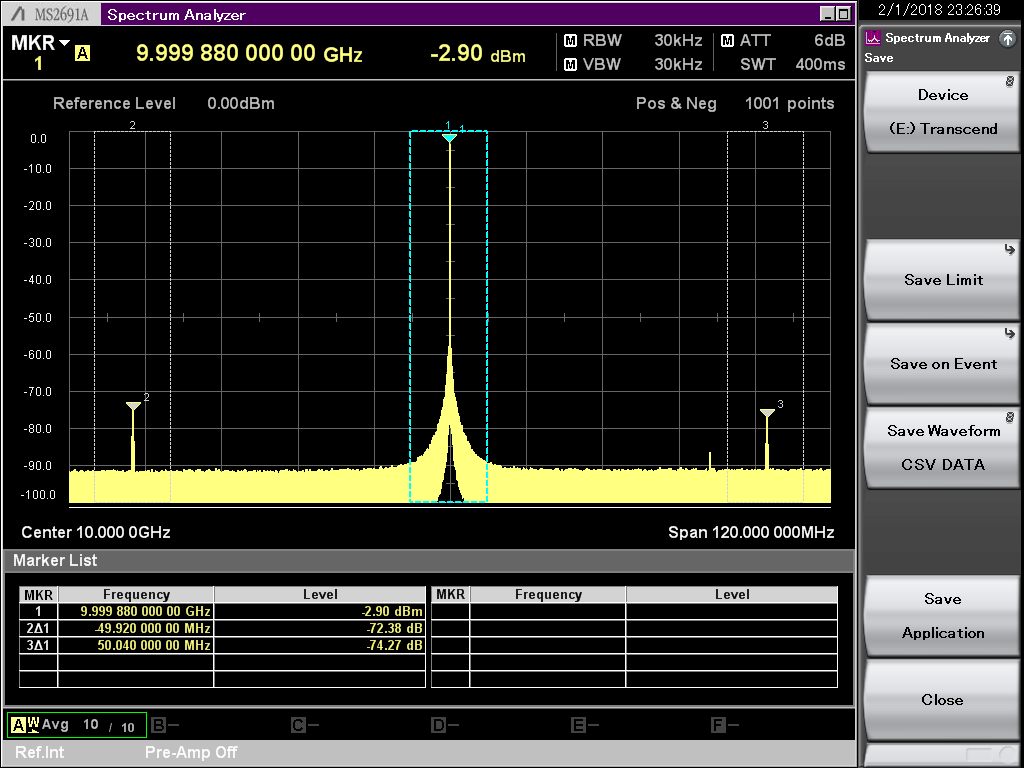

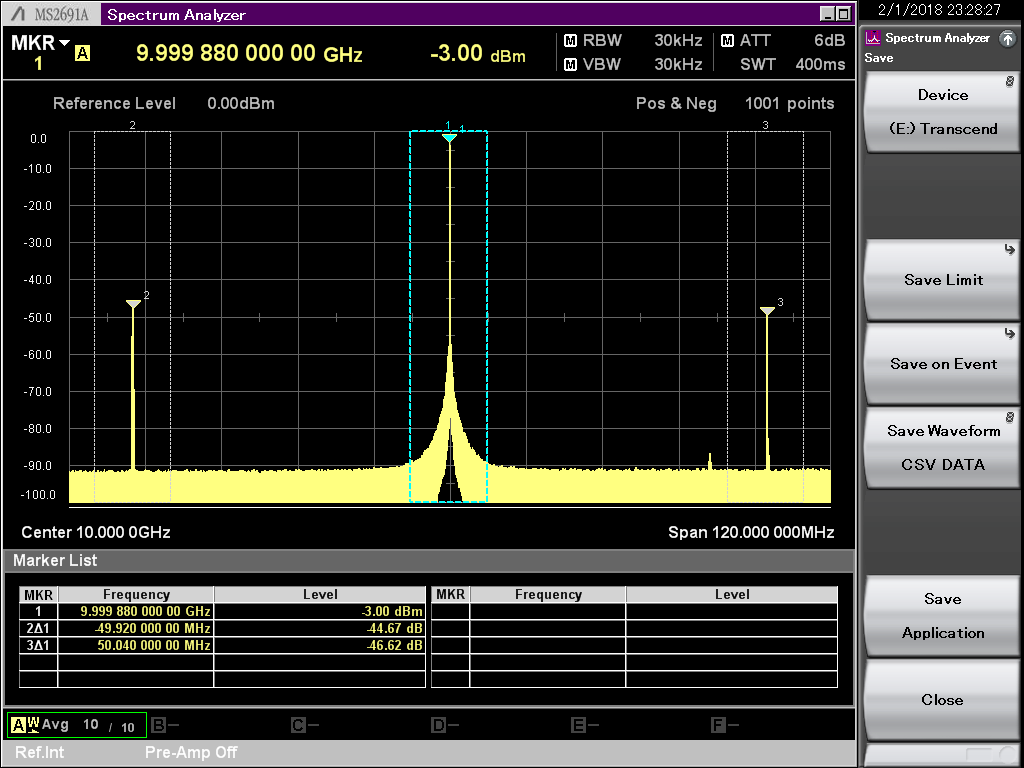

我遇到了一个我不完全理解的问题,也没有找到任何有关该问题的进一步信息。 我将一个100 MHz Ref CLK输入到PLL并在输入路径中除以2,以获得50 MHz的PFD。 之后,我以10GHz的速度操作PLL输出(A或B,无关紧要),因此没有启用输出分隔器。 在PFD的距离处,频谱分析仪中有两个明显的突起,仅向下50-60dBc。 在咨询PLLatinum SIM后,它告诉我这一刺激是由于PFD-VCO串扰! 有人能解释一下这种类型的刺探,或者让我继续阅读吗? 此外,是否有办法减少这些刺激?

谢谢,致以诚挚的问候

Fabian