大家好,

我们是否有关于持续输出电流,IOH和IOL的信息?

提前感谢您的参与。

标记

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好,

我们是否有关于持续输出电流,IOH和IOL的信息?

提前感谢您的参与。

标记

Mark,您好!

如果将时钟同时输入LVCMOS输入和差分时钟输入,则串扰的影响将最小化。

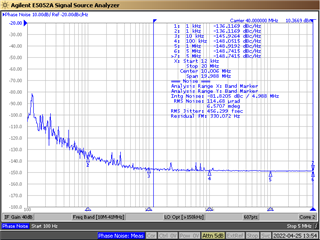

当只有差分时钟被馈入CLK输入引脚时,输出时钟相位噪声将如下所示。

只有CLK输入提供时钟:

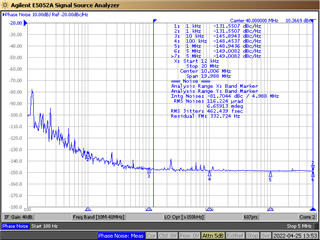

当LVMCOS输入和CLK输入都是FED时钟时,输出时钟相位噪声将如下所示。

CLK输入和LVCMOS输入都被馈入时钟:

如您所见,在这两种情况下相位噪声性能都非常相似,并且rms抖动仅增加约5 FS。

另请注意,这些测量值是使用来自信号发生器的嘈杂时钟输入进行的。 使用性能更好的输入将导致性能更好的输出。

此致,

Kia Rahbar