您好,

我们在新项目中使用了LMK0.4828万,并且我们对此设备存在以下问题:

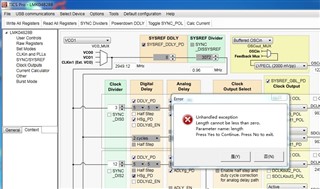

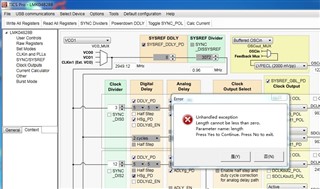

1.我们使用TIC pro来设置LMK0.4828万,错误如下所示:

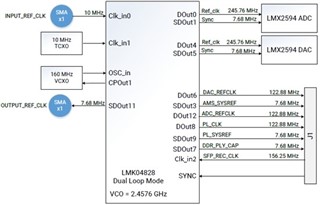

2.请告知如何在CLK下方设置,谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

我们在新项目中使用了LMK0.4828万,并且我们对此设备存在以下问题:

1.我们使用TIC pro来设置LMK0.4828万,错误如下所示:

2.请告知如何在CLK下方设置,谢谢。

您好,Derek,

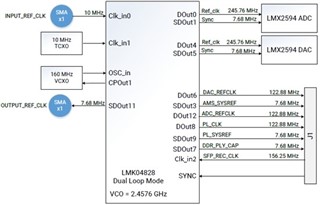

附加以供您评估,谢谢。

张

我在代码中确定了三个可能会引起您描述的错误的地方:

您尝试了以下哪一项?

---

我已经查看了您的配置请求,在继续之前我有一些意见:

此致,

Derek Payne

您好,Derek,

关于第2条,请参阅以下答复: