主题中讨论的其他部件: LMK0.4832万, LMK1D1204

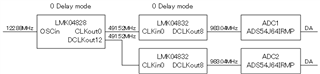

比较LMK0.4828万+ LMK0.4832万+ ADC (ADS54J64IRMP)采集的数据。

即使SPI是在打开和关闭电源后设置的(每次参数都是一致的,并且两个器件之间的参数是一致的),ADC2与ADC1的相位基本上是相同的相位差异。 ,有一些波动。

我想知道这种轻微波动是否在容许范围内,但我应该如何考虑呢? (抖动?,歪斜?)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

比较LMK0.4828万+ LMK0.4832万+ ADC (ADS54J64IRMP)采集的数据。

即使SPI是在打开和关闭电源后设置的(每次参数都是一致的,并且两个器件之间的参数是一致的),ADC2与ADC1的相位基本上是相同的相位差异。 ,有一些波动。

我想知道这种轻微波动是否在容许范围内,但我应该如何考虑呢? (抖动?,歪斜?)

您好,用户123.7122万:

首先,ADC各阶段之间的所有差异实际上都是由偏斜造成的。 使用干净的输入参考时,LMK0.4828万和LMK0.4832万的抖动作用可忽略不计。

假设DCLKout8作为LMK0.4832万零延迟反馈在内部反馈,则LMK0.4832万的零延迟配置可确保 两个不同器件的DCLKout8输出之间的紧密相位对齐 ,只要LMK0.4828万的两个491.52MHz时钟也处于相位。 保证LMK0.4828万的两个491.52MHz时钟处于相位的唯一方法是同步LMK0.4828万, 因此,除非输出时钟在启动和LMK0.4828万编程期间的某个时间点与相同的数字延迟编程同步,否则由于定时不确定设置具有SPI编程的信道分隔器,电源循环之间可能会出现显著的相位变化。

另外,假定LMK0.4828万同步以满足LMK0.4832万的对齐要求, 则两个系统之间会有少数相位误差源:

时钟设备造成的变化幅度似乎比ADC之间的潜在变化幅度小得多。 但是,时钟设备的偏移影响是不可忽略的。 我可以看到几种减少偏移的方法:

此致,

Derek Payne