晚上好。

我在 LMX2492上收到的寄存器编程不一致、我希望您能提供一些见解。

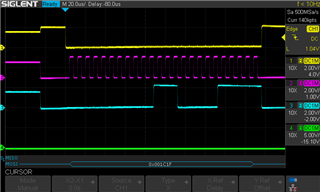

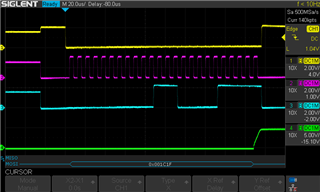

下面是两次编程的相同命令、它从之前的0x0值将增益寄存器0x1C 编程为0x1F。 SCLK 速度为125kHz。

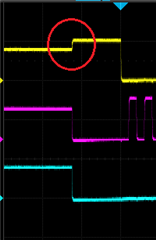

通道1 -锁存使能

CH2 -时钟

CH3 -数据

CH4 -增益输出

它们是一个接一个完成的。 如您所见、在增益上升的情况下、编程"花费"在第二条命令之后。

我似乎没有违反芯片的任何时序规则、有时需要3或4个命令才能实际执行。 我的压摆率比建议的30V/us 快得多(在更好的示波器上检查)。 我的电压高电平高于1.4V 最小阈值。

这里是否有我不遵循的寄存器编程程序? 数据表似乎没有指明任何具体内容。

谢谢、

Nicholas