Other Parts Discussed in Thread: LMK04821, LMK04821EVM

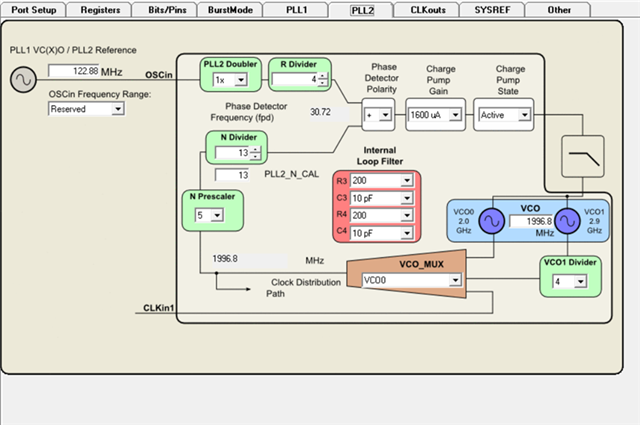

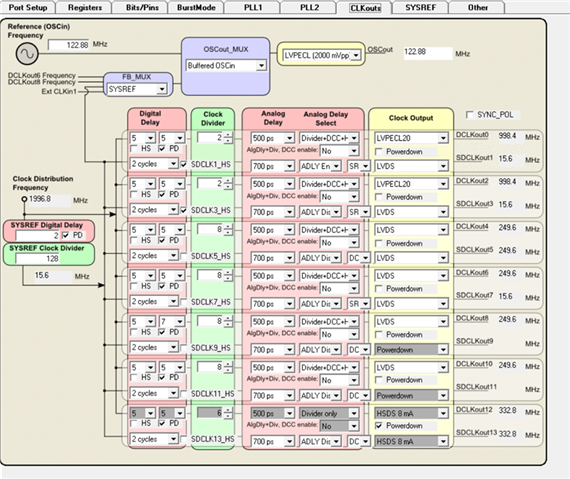

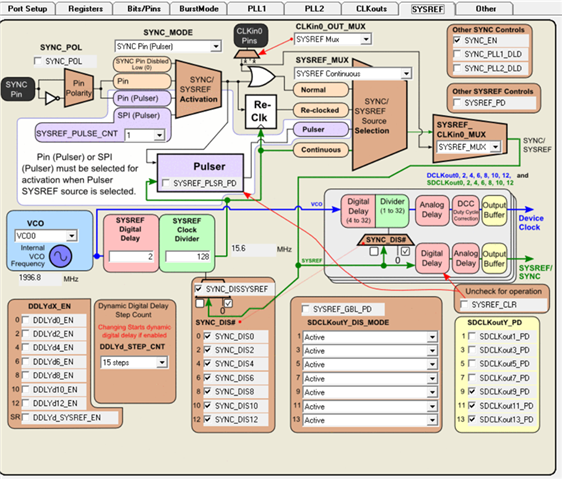

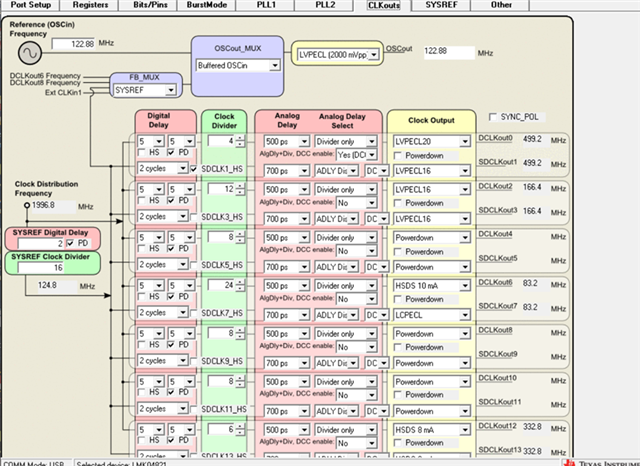

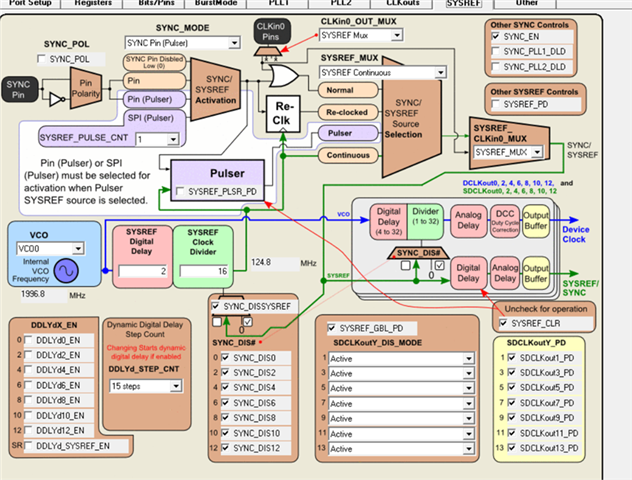

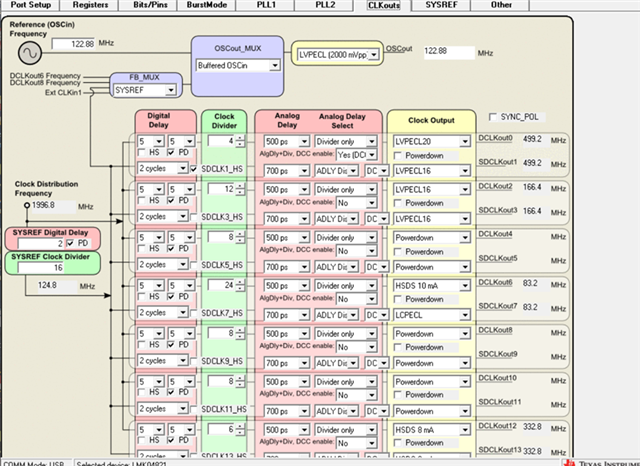

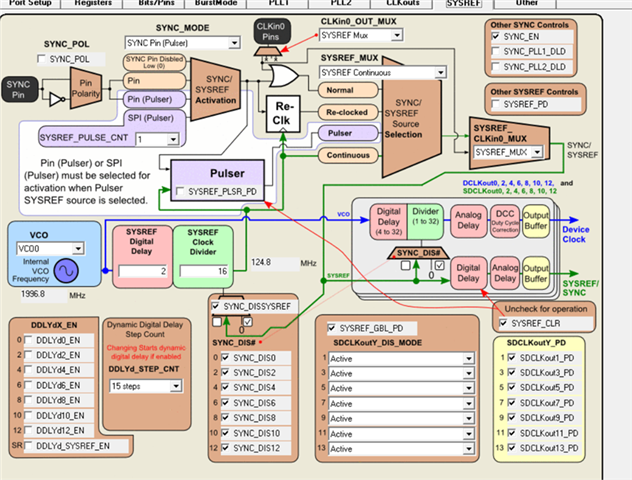

本手册解释了 lmk04821总共有七组时钟。 每组时钟包括 DCLK 和 sdclk、其中 DCLK 受时钟分频器参数影响、另一个 sdclk 受 sysref 时钟分频器参数影响。 在调试期间、发现同一组时钟中的输出波形只受时钟分频器的影响。 配置如下。同轴电缆连接分别为 dclk0和 sdclk1。使用 LMK04821EVM 进行测试。

配置如下所示。

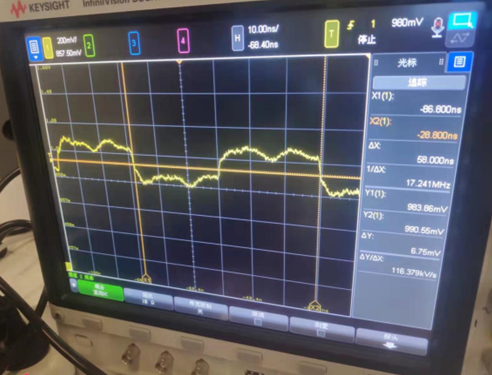

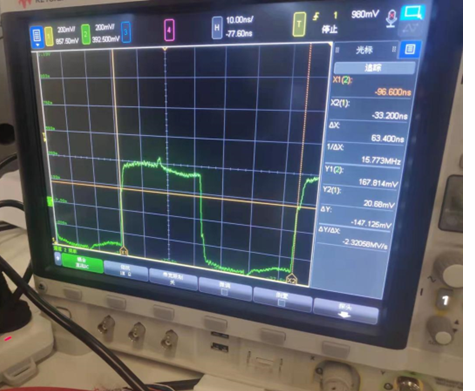

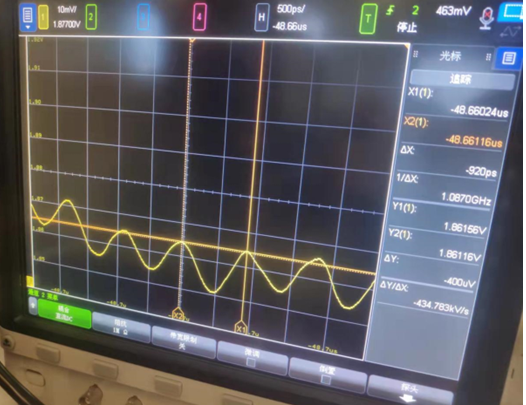

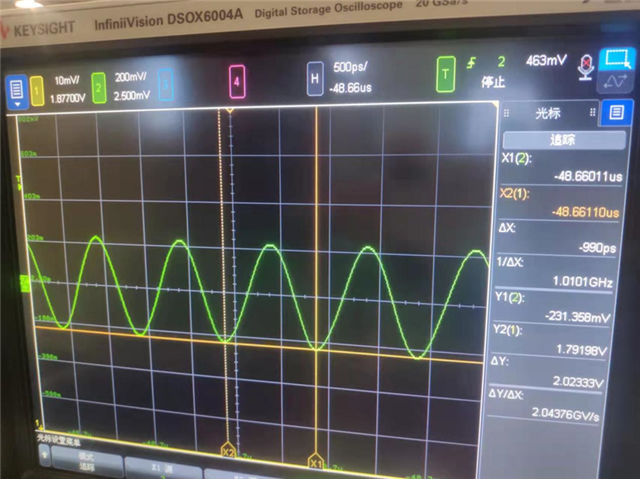

波形如下:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: LMK04821, LMK04821EVM

本手册解释了 lmk04821总共有七组时钟。 每组时钟包括 DCLK 和 sdclk、其中 DCLK 受时钟分频器参数影响、另一个 sdclk 受 sysref 时钟分频器参数影响。 在调试期间、发现同一组时钟中的输出波形只受时钟分频器的影响。 配置如下。同轴电缆连接分别为 dclk0和 sdclk1。使用 LMK04821EVM 进行测试。

配置如下所示。

波形如下:

配置接口如下所示、txt 寄存器文档在寄存器导出接口中被导出、并被写入 FPGA 的 ROM COE 文件中进行读取和写入操作。

每个时钟可以大致输出、但频率会发生变化。

,组分别为1g 和15.6m μ m

EVM 评估板的时间为990ps 和63.4ns (绿色)、

测试板的时间为920ps 和58ns

两个电路板的工艺、材料和温度各不相同。 您是否想询问相关问题的方向。

现在是1996米。 如果调整为2G、是否有针对整个时钟的参考配置。