您好!

我的客户使用的 LMK03806具有以下设置。

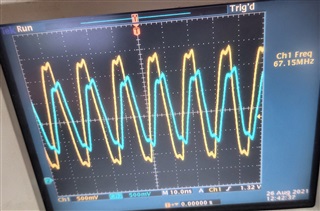

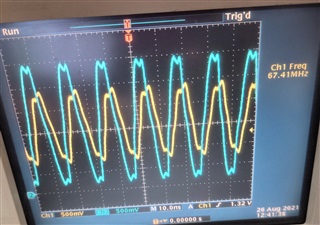

LVCMOS (正常/低)输出的捕捉图像如下(黄色=P 端口/蓝色=N 端口)。

他们认为 N 端口输出为低电平、但有时钟输出。

请帮助我们解决此问题的原因以及解决方法。

谢谢你。

JH

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、JH、

我明天可以再次检查、但我将检查不同的 LVCMOS (设置 P、设置 N)、以查看是否存在一些错误标签。

-是否尝试过其它 LVCMOS 设置?

如果这不是 LVCMOS 设置中的简单错误...

您能更详细地描述测试设置吗? 我注意到、波形与预期的其他方向对齐或180度异相。 是否使用不同长度的电缆?

您能否确认测量是在 EVM 还是其他客户电路板上进行?

-如果是客户电路板、您是否有输出的原理图/PCB?

-我注意到 N 振幅较小。 我想知道是否有一些耦合或100欧姆差分端接导致测得的 N 输出显示波形?

73、

Timothy

您好、Timothy、

感谢您的帮助、

此问题已通过客户设计的电路板得到确认、原理图可在下面的螺纹中找到。

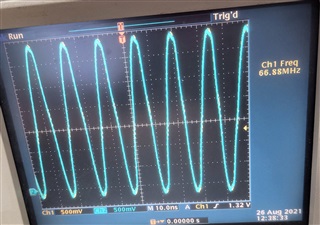

他们还使用不同的问候检查了 LVCMOS 输出。

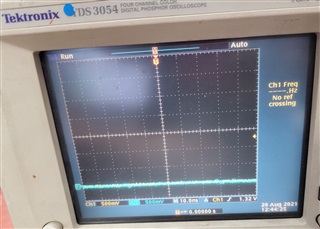

1. LVCMOS (标准/反相)

2. LVCMOS (低电平/低电平)

3. LVCMOS (标准/标准)

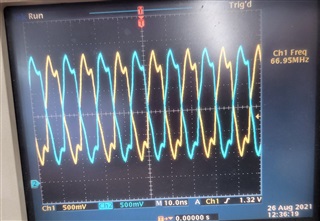

只有一个输出设置发生此问题:LVCMOS (低电平/正常电压)、LVCMOS (低电平/反电压)、LVCMOS (正常/低电平)、LVCMOS (反电平/低电平)。

这是 LVCMOS (低电平/反电平)设置的情况。

此致、

JH

您好、JH、

我确认正常/关闭逻辑没有问题。 原理图审阅将 OUT6显示为 LVDS。 我的期望是布线作为差分布线(因为它似乎是针对 LVDS 布局的)、并且从 CLKout6_P (正常)到 CLKout6_N (关闭)存在大量串扰。

如果您要将频率从61.44MHz 降低到6.144MHz (或更低)、我想您会看到关闭输出的运行方式与预期的相同。

73、

Timothy