大家好、

客户正在其应用中使用 I2C 标准模式(100kHz)、但测试出 I2C SDA/SCL 输入上升时间超过500ns。 详细的测试波形如下所示:

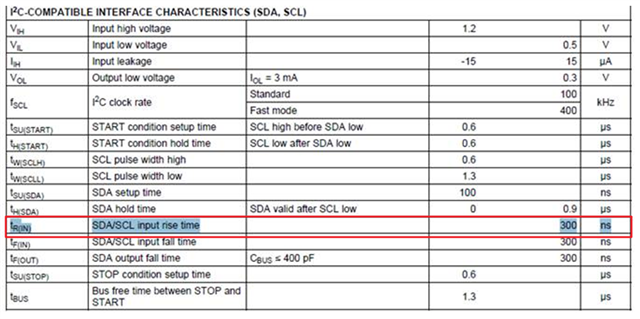

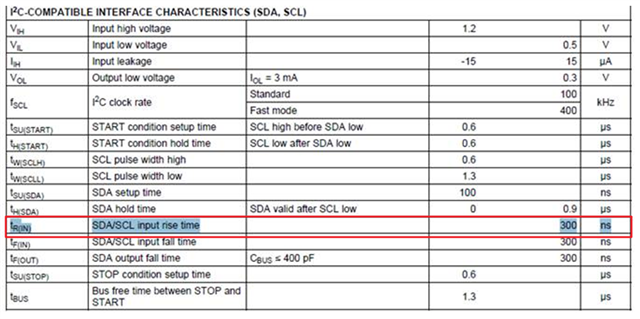

但我们的 D/S 指示最长上升时间应小于300ns。 此处是否存在客户应用的潜在风险? 谢谢。

最棒的

斯坦利

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

客户正在其应用中使用 I2C 标准模式(100kHz)、但测试出 I2C SDA/SCL 输入上升时间超过500ns。 详细的测试波形如下所示:

但我们的 D/S 指示最长上升时间应小于300ns。 此处是否存在客户应用的潜在风险? 谢谢。

最棒的

斯坦利

您好、Stanley、

很抱歉耽误你的时间。

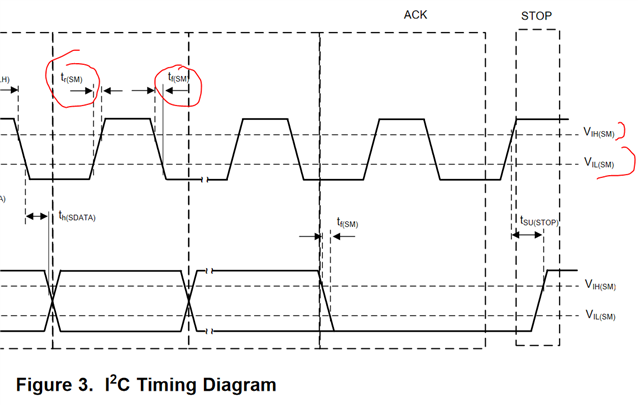

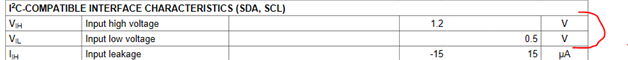

为了正式满足该规范、它不是10%至90%的压摆率、而是从 VIL 到 VIH 的时间、即= 0.5V 至1.2V 或从1.2V 下降到0.5V 通常、10%至90%的压摆率比20%至80%慢得多、在3.3V 系统情况下、0.5V 和1.2V 为15%至36%。 对于1.8V 系统、该值为28%至67%。 因此、为了检查合规性、客户需要测量此范围内的上升/下降。

它认为主要问题是确保数据边沿在时钟边沿之前转换到适当的状态。 因此、压摆率有助于确保数据完整性。

希望这对您有所帮助。

73、

Timothy