主题中讨论的其他器件:LMK04803、 LMK04832

您好、支持团队、

我们计划使用 LMK04803时钟合成器 IC 为 TLK2711 SERDES 收发器提供参考时钟。 我正在寻找可用作参考的 LMK04803评估板的原理图。 我在网站上找不到它、您能提供同样的吗? 此外、当将 LMK04803用于 TLK2711 SERDES 时钟时、您是否可以提供需要记住的任何建议、这对我们非常有帮助。

我们考虑采用 LMK04803、因为它具有高达111毫微微秒的极低 RMS 抖动

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、支持团队、

我们计划使用 LMK04803时钟合成器 IC 为 TLK2711 SERDES 收发器提供参考时钟。 我正在寻找可用作参考的 LMK04803评估板的原理图。 我在网站上找不到它、您能提供同样的吗? 此外、当将 LMK04803用于 TLK2711 SERDES 时钟时、您是否可以提供需要记住的任何建议、这对我们非常有帮助。

我们考虑采用 LMK04803、因为它具有高达111毫微微秒的极低 RMS 抖动

您好!

我找到了评估板说明中的原理图。 我对 LMK04803时钟合成器的使用有一些疑问、如下所示。

LMK04803B 的输出频率要求为110MHz。 我已经使用时钟设计工具尝试了不同的组合来生成110MHz LVCMOS 输出。

我计划将相同频率的 VCXO 用于 PLL1输入和 PLL2输入、参考数据表中的标准122.88MHz 晶体(商业 VCXO 用途)。

对于110 MHz LVCMOS 系列,在较低的标准频率下:20,10,19.8 MHz 是可能的,而对于较高的标准频率,可以是60 MHz,220 MHz。

我的主要目的是选择基准输入源,该基准输入源又可以在110MHz LVCMOS 输出时具有尽可能低的抖动。(如冷冻机122.88MHz 振荡器的数据表中所示)。

我在商用 VCXO 中发现,对于较低的频率(如20MHz),抖动性能不是很好。 在高频率下,可以获得良好的 rms 抖动性能。

因此、为了使110MHz LVCMOS 输出的最终 RMS 抖动在111femto 秒范围内、建议的参考时钟应该仅为高电平、 例如220 MHz,或者使用20 MHz 的低频时钟源是否可以实现111毫微微秒的低 rms 抖动?

请您与我们分享您在时钟源(频率方面)选择方面的指导和支持、以便我们能够为 LMK04803的最终时钟输出实现超低 rms 抖动性能。

您好、Maitry、

很抱歉耽误你的时间。

您将为 PLL1提供什么输入频率。

如果您需要110MHz 输出、则不建议将122.88MHz VCXO 用于 PLL1并用作 PLL2的输入。 对于110MHz 输出、您需要在 PLL2上使用1980MHz VCO 频率。 这样、您就可以使用110或99MHz VCXO。

请注意、LMK0480x 系列中的两个 PLL 都是整数 N PLL。

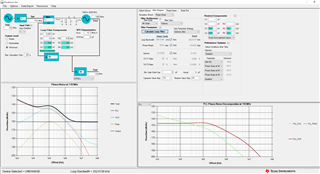

借助 LMK04803、您将在110MHz 时钟下实现大约140fs 的 rms 输出抖动:

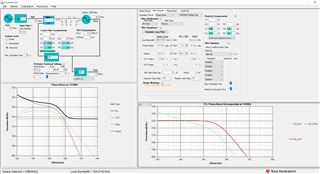

LMK04832可让您低于100fs rms (10kHz 至20MHz):

此致、

Julian

您好!

对于 LMK04803, 我从您的回答中了解到,我们需要在 PLL2的输入和 PLL1的输入(参考时钟)上使用110MHz 商用可用 VCXO,我们可以从 crystek 使用它,

通过在双 PLL 模式下使用 LMK04803、可以获得140飞秒的抖动。

或者、我们能否通过将 PLL1断电来仅使用 PLL2以在单 PLL 模式下使用 LMK04803?

请分享您的观点。