主题中讨论的其他器件: LMK04828、 ADC12DJ5200RF、 LMK04821

大家好、

我的客户正在使用 LMK04826为 FPGA 提供 JESD204C REFCLK、但 JESD204B 链路出现了一些问题、

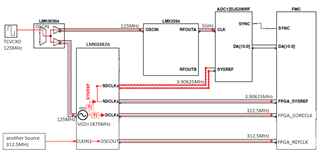

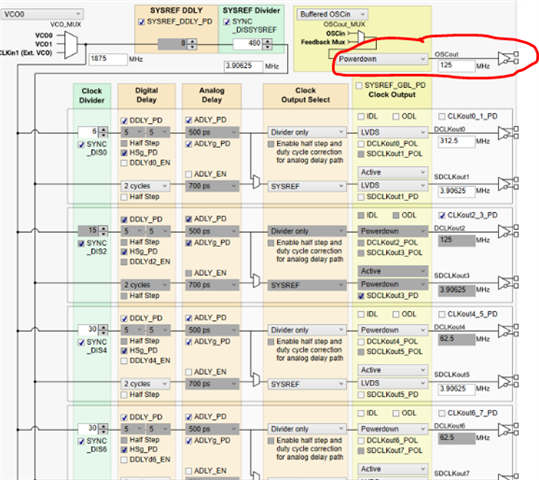

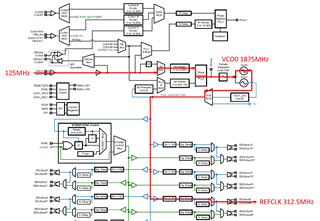

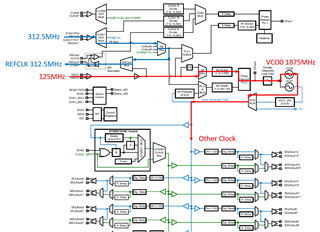

1. 原始设计(参考 至 图片):

FPGA:ZCU106

时钟发生器:LMK04826

来源:TCVCXO 125MHz

VCO0:1875MHz

REFCLK:VCO0/6=312.5MHz

同步问题(参考 :使用上述设置可将 REFCLK 提供给 FPGA,但同步 波形是切换的,无法获取 JESD204C 链接

2.客户修改下面的 LMK04826设置

FPGA:ZCU106

时钟发生器:LMK04826

源:信号发生器312.5MHz

VCO0:未使用

REFCLK:信号发生器旁路= 312.5MHz

结论:提供 REFCLKt o FPGA、同步始终为高电平、JESD204C 变为链接

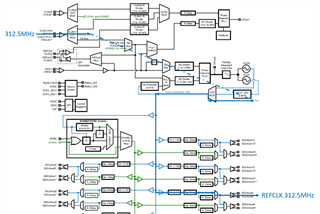

3. 将我们的设计修改为以下设置(参考 图片):

FPGA:ZCU106

时钟发生器:LMK04826

来源:TCVCXO 125MHz 和信号发生器312.5MHz

VCO0:1875MHz

REFCLK:信号发生器旁路= 312.5MHz

结论:为 FPGA 提供 REFCLK、同步始终为高电平且 JESD204C 变为链接

以下是客户提出的问题、

1.为什么312.5MHz REFCLK 除以 VCO0会导致 JESD204C 同步。 无法建立切换和链接?

2.根据#3修改, 125MHz 和312.5MHz 是否需要同步?

客户查看 我们的 ADC12DJ5200RF EVM+ TSW14J57参考设计、REFCLK 也不是 LMK04828 VCO 的分频器、对吗?

谢谢、此致

Eddie