主题中讨论的其他器件:、 LMK05318

大家好、团队、

请帮我解决 LMK05318B 的问题吗?

我们打算使用该电路来清除在超长传输结束时恢复的10MHz 的噪声时钟信号。 具有模拟 PLL 和 BAW VCO 的电路应该是非常好的解决方案、如应用报告 SNAA326中所述。

为了进行评估、我有一个 LMK05318BEVM 板、它具有 TICS Pro 固件 v1.7.2.0

通过 GUI:

DPLL 被禁用、以便仅使用 AnalogPLL 1。

XO 设置为10MHz、单端接口、我将10MHz 0dBm 信号连接到 XO 连接器。

在设置输出频率计划中、输出设置为10MHz、我 可以在所有激活的输出上看到10MHz 信号。

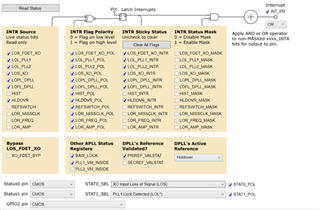

在以下配置中,在 XO 输入信号丢失后,Status0 LED 将被打开和关闭,但我找不到任何解决方案来指示使用 status1 LED 检测到的 PLL1锁定

我尝试 更改原始寄存器,但没有成功。

当 I CUT XO 上的10MHz 信号时、0xD 寄存器中的位2 (LOL_PLL1) ET 4 (LOS_FDET_XO)将变为1、但状态1保持为1时没有任何变化

当我更改连接到 XO 的发生器的频率时,这些位保持高电平,这应该表明 PLL1保持锁定,无论 XO 连接器上施加的频率是多少?

请注意、在所有配置中、信号会保持存在、并在激活的输出上稳定在10MHz

非常感谢您的帮助

Christian