Other Parts Discussed in Thread: LMK04826, LMK04832, LMK04832EVM

主题中讨论的其他器件: LMK04832、 LMK04832EVM

尊敬的先生/女士:

我们打算在 产品中使用 LMK04826BISQ/NOPB 器件、我们有以下一些查询

我们能否为 FPGA 生成250MHz 时钟。

2.我们能否在14个输出中从该器件生成50mHz 时钟。 如果是、请告诉我们频率稳定性。

此致、

Sunil Kumar

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: LMK04826, LMK04832, LMK04832EVM

尊敬的先生/女士:

我们打算在 产品中使用 LMK04826BISQ/NOPB 器件、我们有以下一些查询

我们能否为 FPGA 生成250MHz 时钟。

2.我们能否在14个输出中从该器件生成50mHz 时钟。 如果是、请告诉我们频率稳定性。

此致、

Sunil Kumar

您好、Sunil、

1.是的、LMK04826的输出频率范围为225kHz 至2505MHz。

2. 是的、LMK04826的输出频率范围为225kHz 至2505MHz。 频率稳定性可通过以下公式计算得出:

PLLx_WND_SIZE 始终设置为2 (窗口大小为3.7ns)。 fPDx 是用于 PLL 的相位检测器频率、对于 PLL1、该值介于0至40MHz 之间、对于 PLL2、该值介于0至155MHz 之间。 PLLX_DLD_CNT 的值可以介于1至16、383之间。

此致、

起亚拉赫巴

HII Kia Rahbar

感谢您的快速响应。

我对同一器件有一些疑问、请帮助我们。

因为我们将从 LMK04826BISQ/NOPB 为设计中的其他块生成8个时钟。

我列出了时钟频率表。

| PLL 引脚名称 | 引脚编号 | 时钟组 | 时钟使用的器件 |

| DCCLKOUT2 | 15. | 时钟组1 | AFE5816ZAV CW 时钟频率为16X 8MHz |

| DCCLKOUT2* | 16. | ||

| SDCCLKOUT3 | 13. | 时钟组1 | AFE5816ZAV CW 时钟频率1X 2MHz |

| SDCCLKOUT3* | 14. | ||

| SDCCLKOUT5 | 22. | 时钟组2 | XC7A200T-1SB484I FPGA 250MHz |

| SDCCLKOUT5* | 23 | ||

| DCCLKOUT4 | 24 | 时钟组2 | AFE5816ZAV ADC 时钟5至80MHz |

| DCCLKOUT4* | 25 | ||

| SDCCLKOUT9. | 49 | 时钟组3 | AD9102BCPZ DAC_1 50MHz |

| SDCCLKOUT9* | 50 | ||

| DCCLKOUT10 | 54 | 时钟组3 | AD9102BCPZ DAC_2 50MHz |

| DCCLKOUT10* | 55 | ||

| OSCout | 40 | OSCout 组 | ADIN300BCPZ-R7 以太网_1 25MHz |

| OSCout* | 41. | ADIN300BCPZ-R7 Ethernet_2 25MHz | |

| CLKIN1_FIN_FBCLKIN | 34 | 时钟输入(参考时钟) | 125 M Hz 晶振 |

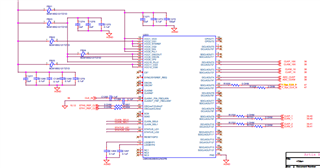

器件原理图:

我请求您确认 LMK04826BISQ/NOPB 能够在 运行过程中不中断地生成这些时钟。

寻求快速响应。

此致、

Sunil。

您好、Sunil、

LMK04826具有7个 DCLK 分频器(1至32 div 值)和1个 SYSREF 分频器(8至8191 div 值)。

因此、对于所需的时钟频率、它可以生成具有2500MHz VCO 频率的250MHz 输出、并且可以使用 SYSREF 分频器(大于32)生成其余任何一个频率、但不能同时生成所有频率。

使用 DCLK0和 SDCLK1等相同的通道组、可以在两个通道上生成相同的 DCLK 频率或 DCLK 频率和 SYSREF。

您是否打算在双 PLL 抖动清除器模式下或仅在单个 PLL 中使用 LMK04826来生成多个频率?

在双 PLL 模式下、OSCin 需要 VCXO/晶体来为 PLL2生成 REFin、同时在 CLKin1输入端生成外部基准。 在单 PLL 模式下、外部基准(125MHz)应该在 OSCin 输入上提供。

为了生成所有所需的频率、我建议使用 LMK04832、该器 件与 LMK0482x 器件引脚兼容、并具有 DCLK 分频器(1至1023 div 值)和 SYSREF 分频器(8至8191 div 值)。 可使用 SYSREF 分频器生成2MHz 时钟输出。

希望能澄清您的疑问。

如果您需要进一步的帮助、请告知我们。

谢谢!

此致、

Ajeet Pal

HII Ajeet Pal、

感谢您的重播、我们不了解时钟抖动主题、因此请帮助我们澄清以下问题。

LMK04826具有7个 DCLK 和7个 SDCLK。

因为我们在设计中需要7种不同的时钟频率。 我认为、借助该器件、我们可以使用7个 DCLK 通道在不产生任何问题的情况下生成该器件。 请确认我们的理解是否正确。

2.就上述点而言,我们需要8MHz、250MHz、80MHz、50MHz、50MHz 作为差分时钟。 我们能否使用 DCLKout0、 DCLKout2、 DCLKout4、DCLKout6、 DCLKout12、 DCLKout10生成这些频率。 请遵守。

注:如果上述配置中出现错误、请帮助我们提供详细说明。

我们需要两个 LVDS 格式的时钟输出、两个通道的频率约为50MHz。

参考 LMK04826数据表 9.1.9时钟分配部分。 OSCout 可以是 OSCin、DCLKout6、DCLKout8或 SYSREF 的缓冲版本。 我们计划将 OSCout (引脚编号40和41)用作 LVDS 对。

我们假设 DCLKout6缓冲区版本 是 OSCout。 因此、我们可以在程序中进行修改。 请确认此部件。

4.请告诉我们在 DCLK 输出通道中可以生成的最小时钟频率是多少。

寻求快速响应。

此致、

Sunil

您好、Sunil、

[引用 userid="501123" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1043660/lmk04826-lmk04826/3872688 #387268"]LMK04826具有7个 DCLK 和7个 SDCLK。

因为我们在设计中需要7种不同的时钟频率。 我认为、借助该器件、我们可以使用7个 DCLK 通道在不产生任何问题的情况下生成该器件。 请确认我们的理解是否正确。

[/报价]是的、LMK04826可以生成7个具有最大分频值32的 DCLK 频率。

[引用 userid="501123" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1043660/lmk04826-lmk04826/3872688 #387268"]2.就上述点而言,我们需要8MHz、250MHz、80MHz、50MHz、50MHz 作为差分时钟。 我们能否使用 DCLKout0、 DCLKout2、 DCLKout4、DCLKout6、 DCLKout12、 DCLKout10生成这些频率。 请遵守。

注:如果上述配置中出现错误、请帮助我们提供详细说明。

[/报价]如前所述、要使 LMK04826的时钟输出为250MHz、所需的 VCO 将为2500MHz。 因此、除了 SYSREF 分频器外、它不能生成其他所需频率、80MHz (需要 div - 31.25)、50MHz (需要 div - 50)、8MHz (需要 div - 312.5)(整数分频器值高达32)。

[引用 userid="501123" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1043660/lmk04826-lmk04826/3872688 #387268"]我们需要两个 LVDS 格式的时钟输出、两个通道的频率约为50MHz。

参考 LMK04826数据表 9.1.9时钟分配部分。 OSCout 可以是 OSCin、DCLKout6、DCLKout8或 SYSREF 的缓冲版本。 我们计划将 OSCout (引脚编号40和41)用作 LVDS 对。

我们假设 DCLKout6缓冲区版本 是 OSCout。 因此、我们可以在程序中进行修改。 请确认此部件。

[/报价]如果 LMK04826未在零延迟模式下运行、则可以使用反馈多路复用器使用 DCLK6、DCLK8或 SYSREF 信号设置 OSCout、并可以 LVDS 格式或其他格式在 OSCout 引脚上生成输出。 可使用具有所需频率的反馈多路复用器将 DCLK6设置为 OSCout。

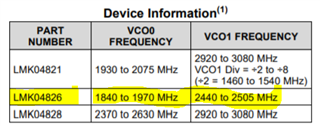

[引用 userid="501123" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1043660/lmk04826-lmk04826/3872688 #387268]4. 请告诉我们在 DCLK 输出通道中可以生成的最小时钟频率是多少。[/quot]在最小内部 VCO 频率(1840MHz)和最大 DCLK 通道分频器(32)的情况下、DCLK 通道的最小时钟输出频率将为57.5MHz。

谢谢!

此致、

Ajeet Pal

尊敬的 Ajeet Pal:

非常感谢您的帮助。

因为我们需要5个不同通道中的所有不同频率。 如前所述、我们无法使用 LMK04826器件生成这些频率。 正如您在之前的电子邮件中提到的、我们计划切换 LMK04832器件。

根据我们从 LMK04832数据表中了解到的、我们可以对 VCO 时钟进行分频 (1到1023 div 值)。 请确认我们的理解正确。 我们可以在专用通道 8MHz、250MHz、80MHz、50MHz、50MHz 中生成该频率。

2.我们需要两个50MHz 时钟源来驱动设计中的两个块。 输出时钟源应为单端 LVCMOS 时钟。 请帮助我们解决这个问题、了解如何使用 LMK04832器件生成。

请说明2个 LVCMOS 的清晰度。 (请解释为什么它是2倍)。 如果我们想使用 LVCOMS 生成的通道之一的 LVCMOS 时钟源、

因为 LMK04832通道中有两个输出如何用于此单端时钟源器件。

因为我们需要为 LMK04832提供参考时钟源。 我们计划使用122MHz 的外部晶体。 请建议我们 在哪里连接晶体、因为我们可以看到数据表中有三个时钟输入。

注意:由于我们处于设计的关键阶段、因此需要快速响应

此致、

Sunil

您好、Sunil、

[引用 userid="501123" url="~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1043660/lmk04826-lmk04826/3873935 #3873935]1. 正如我们从 LMK04832的数据表中了解到的、我们可以对 VCO 时钟进行分频 (1到1023 div 值)。 请确认我们的理解正确。 我们可以在专用通道 8MHz、250MHz、80MHz、50MHz、50MHz 中生成该频率。[/QUEST]没错。 LMK04832支持从1到1023的 DCLK 时钟分频器值。 为了生成所有必需的频率、需要进行适当的频率规划、包括其基准输入。 与125MHz 参考输入类似、考虑到250MHz 的关键所需频率、VCO 频率可以是3000MHz、它可以生成除80MHz 之外的所有所需频率、这会导致其不是3000MHz 的整数分频值。 因此需要更改80MHz 时钟频率。 同样、如果80MHz 是关键时钟频率、则可以选择 VCO 频率3200MHz、该频率可生成除250MHz 之外的所有必需基准输入频率。

[引用 userid="501123" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1043660/lmk04826-lmk04826/3873935 #3873935"]2. 我们需要两个50MHz 时钟源来驱动设计中的两个块。 输出时钟源应为单端 LVCMOS 时钟。 请帮助我们解决此问题、了解如何使用 LMK04832器件生成。LMK04832支持9个时钟输出通道上的 LVCMOS 输出、并可从单通道生成2个数字50MHz 单端 LVCMOS 信号。

[引用 userid="501123" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1043660/lmk04826-lmk04826/3873935 #3873935"]请说明2个 LVCMOS 的清晰度。 (请解释为什么它是2倍)。 如果我们想使用 LVCOMS 生成的通道之一的 LVCMOS 时钟源、

因为 LMK04832通道中有两个输出如何用于此单端时钟源器件。

[/报价]每个差分引脚可被设定为具有 NORM/INV (同相/180deg 异相)的 LVCMOS 输出。 2倍表示每个通道的 LVCMOS 输出数量。 因此、总共可以从9个通道生成18个 LVCMOS 输出。

[引用 userid="501123" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1043660/lmk04826-lmk04826/3873935 #3873935"]4. 因为我们需要为 LMK04832提供参考时钟源。 我们计划使用122MHz 的外部晶体。 请建议我们 在哪里连接晶体、因为我们可以看到数据表中有三个时钟输入。 [/报价]与您的参考时钟频率有点混淆、它是125MHz (在上一条评论中)还是122MHz? 任何频率规划下的方法都需要仔细选择。

LMK04832可灵活地从任何输入提供基准。 如果需要单个 PLL (PLL2)、您可以在 OSCin 引脚上进行连接。 对于双 PLL 模式、您还可以保持在 OSCin 引脚上、并且可以在 CLKin0/CLKin1上提供其他基准。

谢谢!

此致、

Ajeet Pal

HII Ajeet Pal、

非常感谢您的回应!!!!

我们已经对该 LMK04832器件进行了相当清楚的说明。 在我们转向布局设计时、您能不能建议我们在差分对时钟和 LVCMOS 时钟上需要遵循什么阻抗。

我请求您建议我们在时钟信号上遵循 PCB 中的最小和最大布线长度。

因为我们使用差分对的单端 LVCMOS 时钟。 如何在相关通道中配置左侧输出引脚。 我们是否需要保持浮动或拉至高电平或拉至接地。

至于您的实物信息、我们计划使用125m Hz 晶体作为参考时钟。

此致、

Sunil Kumar

您好、Sunil、

[引用 userid="501123" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1043660/lmk04826-lmk04826/3875544 #3875544"]我们已经对该 LMK04832器件进行了相当清楚的说明。 在我们转向布局设计时、您能不能建议我们在差分对时钟和 LVCMOS 时钟上需要遵循什么阻抗。

我请求您建议我们在时钟信号上遵循 PCB 中的最小和最大布线长度。

[/报价]以下 Thread 提供了 LMK04832EVM 设计文件 FYR、其中提供了器件布局限制的详细信息和布线详细信息。 器件输出差分对以100欧姆阻抗运行、LVCMOS 布线将以50欧姆单端传输线路运行。 请遵循数据表中提到的布局指南。

[引用 userid="501123" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1043660/lmk04826-lmk04826/3875544 #3875544"]、因为我们使用差分对的单端 LVCMOS 时钟。 如何在相关通道中配置左侧输出引脚。 我们是否需要保持浮动或拉至高电平或拉至接地。 [/报价]对于 LVCMOS、单端线路的布线电阻为50欧姆、未使用的引脚因差分线路而异、未使用的引脚可能会使输出浮动在靠近 IC 的位置。 或者、 如果从器件以差分方式布线、并在未使用布线的末端分流到50 Ω、则在该布线的末端放置一个50 Ω 端接。

[引用 userid="501123" URL"~/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1043660/lmk04826-lmk04826/3875544 #3875544"]对于您的种类信息,我们计划使用125m Hz 晶振作为参考时钟。需要根据参考时钟频率和所需的输出频率进行频率规划、

谢谢!

此致、

Ajeet Pal