您好!

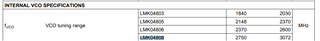

我们尝试使用 LMK04808双环路配置生成500MHz 信号。 但是、我们无法使 PLL1锁定(PLL2处于锁定状态)。

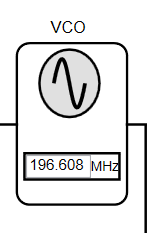

基准输入(CLKin1)是一个125MHz 时钟信号。 我们使用的 VCO 是来自 Abraacon 的200MHz VCXO:https://www.mouser.de/datasheet/2/3/ASG-P-35446.pdf

PLL1 PD 参数:

- 频率:25MHz

- 增益:100uA

- 正极性

PLL1环路滤波器值:

- C1:39nF

- C2:1.8 μ F

- R2:2.2k Ω

有关器件的完整配置、请参阅 TICS Pro 中的十六进制寄存器值: /cfs-file/__key/communityserver-discussions-components-files/48/Dual_5F00_Loop_5F00_config.txt

我们检查了 PLL1 R 和 N 分频器输出频率、这似乎是可以的。

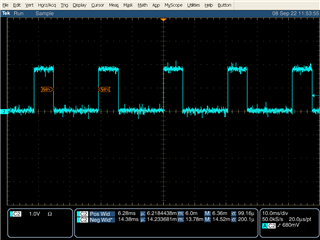

但是、PLL1 DLD 信号如下所示:

我们尝试使用 PD 参数、但这不会明显影响行为。

根据我们的理解、配置应该正常工作。 也许我们还错过了什么?

否则、我们怀疑所选的 VCXO 可能不适合该器件。

您能否帮助我们解决此问题或指明问题可能出在哪里? 如果需要更多信息、请告知我们。

提前感谢、致以最诚挚的问候!

奥莱纳