您好!

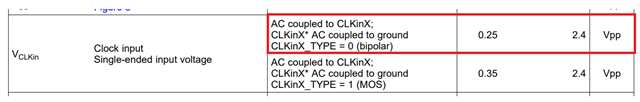

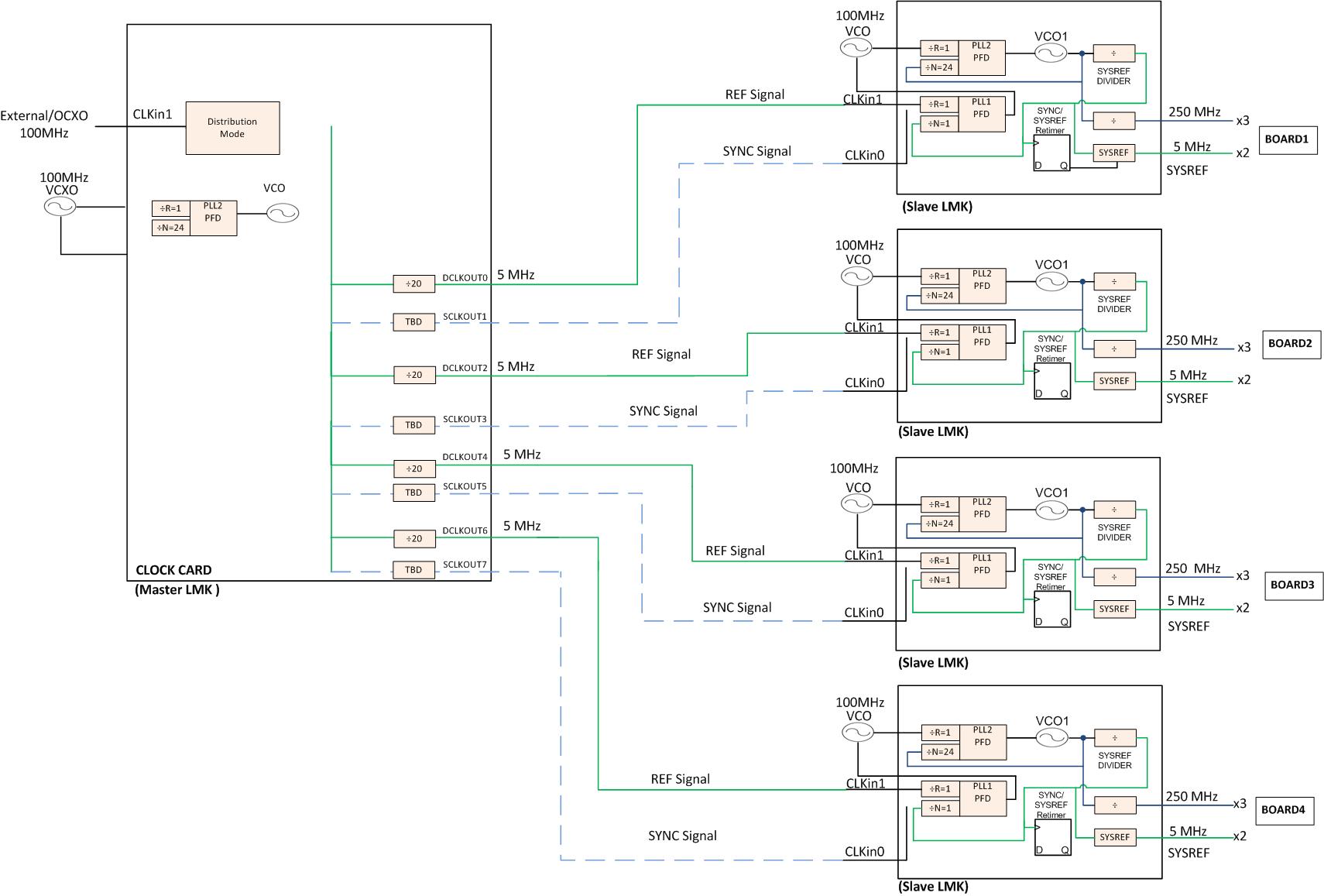

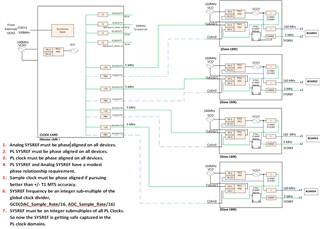

我们计划使用 LMK04828时钟合成器(主从方案)实现 RFSoC FPGA 多板同步。

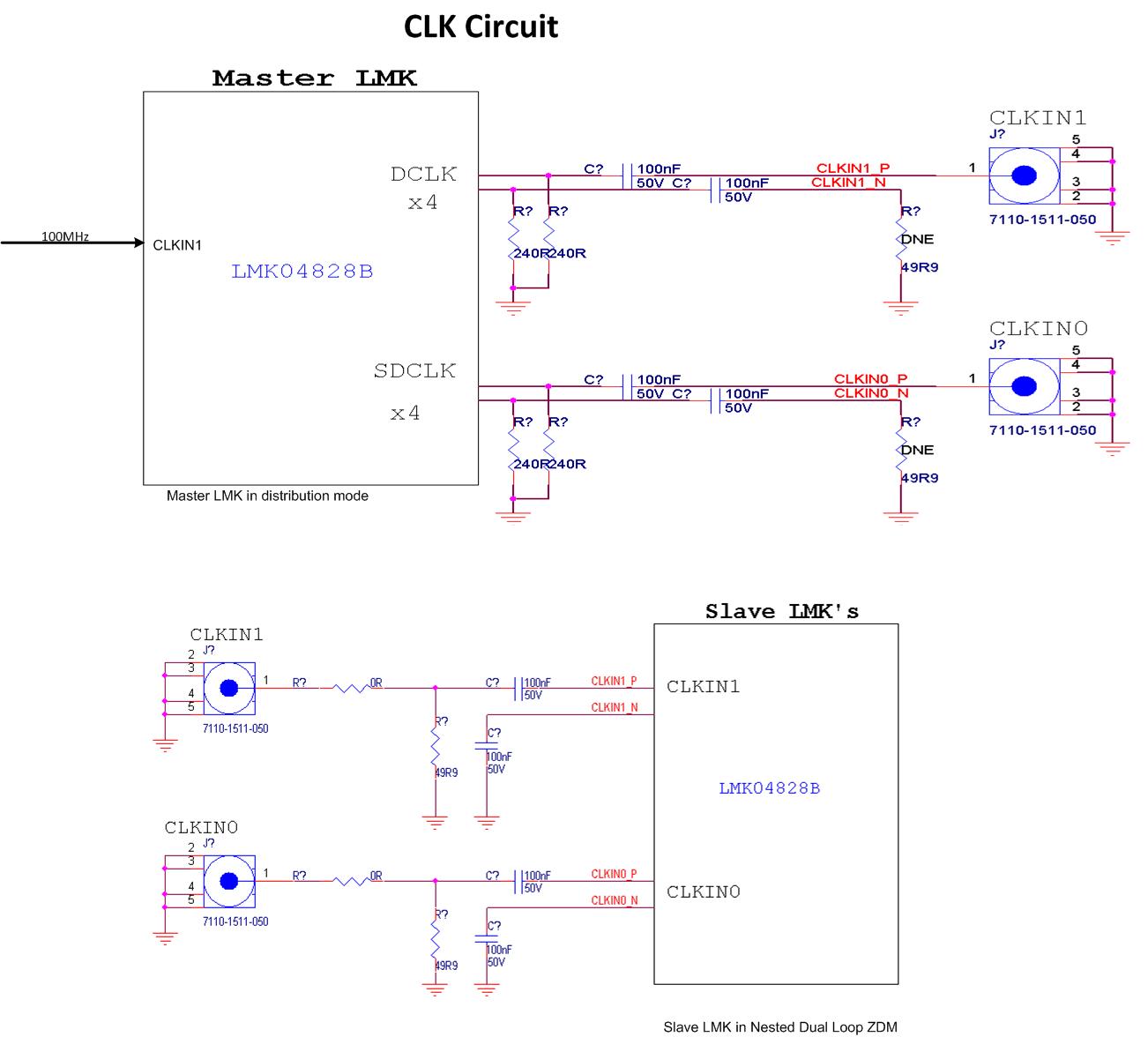

- 主 LMK 将在 CLKIN1上具有来自外部/板载 OCXO (可选)的100MHz 参考时钟。

- 主 LMK 将处于 分配模式、并为从 LMK 生成5MHz 参考时钟。

- 所有从 LMK 将在 CLKIN0处通过匹配的电缆接收来自主 LMK&的5MHz 参考时钟。

- 所有从器件 LMK 都具有到 OSCIN 的160MHz VCXO 输入

- 从器件 LMK 将生成160MHz DCLKOUT 和5MHz SYSREF、以遵循 ZDM 并处于双环路模式。

- 所有4个从 LMK 输出时钟都需要同步和对齐以实现多时钟同步。

请验证以下方案并确认所有从 LMK 都将具有从上电到上电的确定性延迟。

我们将共享配置文件。

。

。