Other Parts Discussed in Thread: LMK61E2

主题中讨论的其他器件:LMK61E2

德州仪器支持部的上午/下午好。

感谢您抽出宝贵的时间为您提供支持。

因此、我知道频率小于原始时钟(2倍或更多)的时钟 存在相位不确定性、除非时钟来自同一分频器

以下是设置:

- UWire 控制和 SYNC0=SYNC1

- Clkin0和 Clkin1均为200MHz 且同步(它们源自可编程 LMK61E2、通过德州仪器(TI) LVPECL 或 LVDS 缓冲 器 CDCLVP2102RGTR 或 CDCLVD2102RGTT)

我希望:

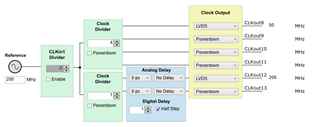

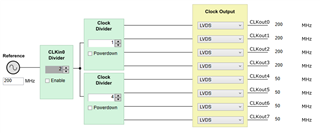

- LVDS Clokc Banka 未分频 CLKout0、 CLKout1、 CLKout2、 CLKout3与最小内部偏斜3ps (PAG 10)同相

- LVDS Clokc Banka 除以4 CLKout4、 CLKout5、 CLKout6、 CLKout7与最小内部偏斜 3ps (PAG 10)、偏斜与上述值同相

- LVDS Clokc Banka 未分频与 VDS Clokc Banka 除以4约400ps 之间的偏差(50MHz https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/859944/lmk01801-output-skew-between-different-divider 的值为真 ,但我不知道在其他情况下是否为真)

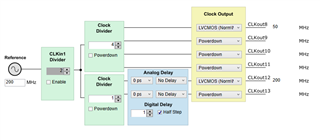

- CLKout8 CMOS 将与 CLKout1处于临时相位关系、它将与 Clokout4的相位不同。

- CLKout12 CMOS 将与 CLKout0具有确定性关系(pahse 0)、因为 SYNC0=SYNC1、Clkin0和 Clkin1具有相同的同步频率(我是不是错?)

- 我需要估算 CLKout12和 CLKout0之间的偏斜。 如果超过 250ps、我无法使用此解决方案。

- 我还需要估算 CLKout8至 CLKout4的偏移、但需要考虑的问题远不那么严格

感谢您抽出宝贵的时间、致以诚挚的问候。