大家好、

你好。

根据我们的客户、 LMK04828评估模块中的单端交流耦合输入(SNAU145B-2013年5月- 2018年3月修订)使用 OSCin_N 和 CLKIN_N 的负输入、而不是正桥臂_P 是否需要"反相"输入连接、或者是否也可以对这些单端信号使用_P 输入?

此外、只需确认交流耦合单端配置中的 OSCin 输入是否可以由3.3V 信号驱动?

谢谢、此致、

艺术

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

你好。

根据我们的客户、 LMK04828评估模块中的单端交流耦合输入(SNAU145B-2013年5月- 2018年3月修订)使用 OSCin_N 和 CLKIN_N 的负输入、而不是正桥臂_P 是否需要"反相"输入连接、或者是否也可以对这些单端信号使用_P 输入?

此外、只需确认交流耦合单端配置中的 OSCin 输入是否可以由3.3V 信号驱动?

谢谢、此致、

艺术

艺术、

它们可以将正桥臂_P 用于任一输入。 OSCin 仅使用_N 输入、因为 VCXO 制造商经常在同一封装中的6引脚封装和4引脚封装之间进行交替、并且 OSCin_N 连接到始终存在的输出引脚。 CLKin1_N 选择是任意的。

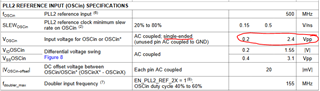

OSCin 最大单端交流耦合信号摆幅为2.4V。 OSCin 缓冲器的设计与 CLKIN 缓冲器略有不同。 超过这些限值的信号摆幅会压缩输入级并增加近端相位噪声。

如果需要使用3.3V 电源驱动、例如 LVCMOS、建议使用电阻分压器来减小信号摆幅。 例如、EVM 上的 R4和 R61形成一个分压器、该分压器将 VCXO 的~3V LVCMOS 输出衰减至大约1V。

此致、

Derek Payne

艺术、

感谢您的提醒 ping、由于某种原因、我没有收到有关此主题的通知。

根据超出建议范围的电压偏移和信号的压摆率、可能会发生一些影响:

数据表中的限制是出于某种原因指定的、客户应尝试遵循这些限制。

此致、

Derek Payne