大家好

如果我们问 LMK03328、您会介意吗?

我们要确认环路带=10kHz 和 环路带=600kHz 之间的锁定时间。

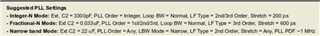

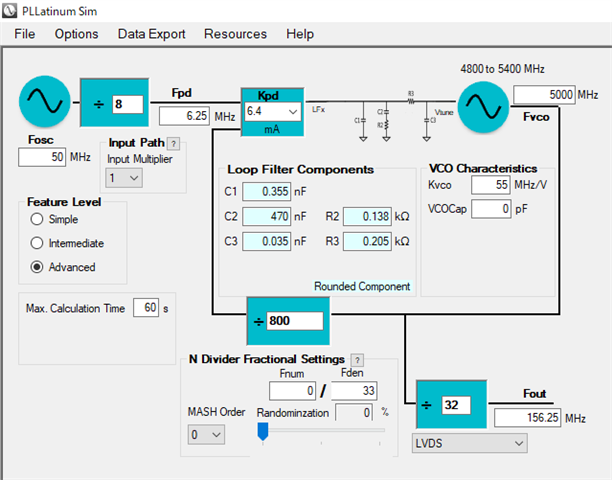

您能否参阅以下图表;

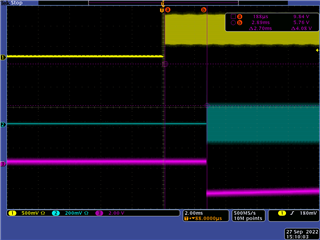

■CH1=REF (外部)、CH2=OUT7、CH3=STAT0 (LOCK)_LBW=10kHz、锁定时间

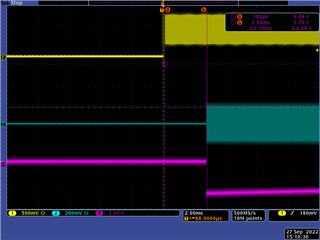

■CH1=REF (外部)、CH2=OUT7、CH3=STAT0 (LOCK)_LBW=600kHz、锁定时间

我们尝试确认在每个环路设置的情况下是否存在差异。

但有一些差异。 行为是否正确?

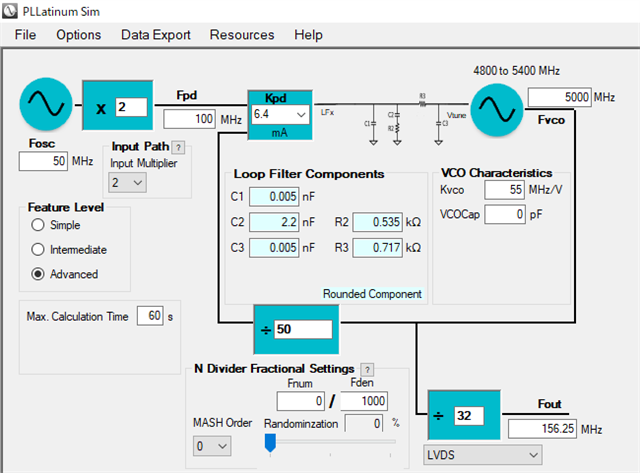

然后、数据表显示了如下所示的"PLL 被锁定且有效输出可用";

在计算过程中、Txo、 Tcal-PLL 和 Tvco2是相同的值。

TLOCK-PLL2 (PLL2锁定时间)是 PLL2的~4/LBW。

如果 LBW = 10kHz:40uS

如果 LBW = 600kHz:1.67us

在图中、时间范围为2ms、因此在 LBW=10kHz 的情况下、锁定时间应缩短。

您可以向我们提供您的意见吗?

此致、

大田松本