概述

我们的 LMK04828设计在启动时间歇性地使 PLL1初始锁定失败。 如果 LMK 从上一个电源周期开始“预热”到大约36°C 的封装温度,我们就能够重现此故障。 如果我们给它加电,并且 LMK 的封装温度为25°C 环境温度,那么 LMK 将实现 PLL1锁定,并且永远不会失去锁定,即使封装温度超过36°C 也是如此 在锁定失败的情况 下、PLL1_DLD、CP1Out 和数字 IO 以某种 MHz 频率振荡。 我们正在寻求 TI 工程师的支持、因为数据表中似乎未定义该行为、并提供了电路原理图、LMK 寄存器设置和示波器截图。

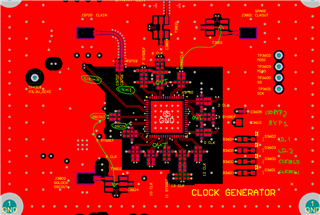

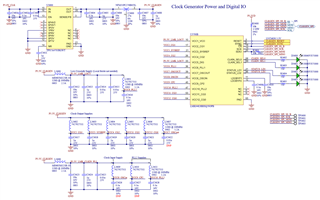

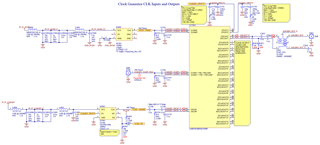

原理图设计

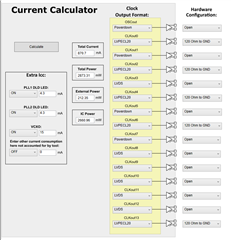

LMK 寄存器设置

e2e.ti.com/.../CurrentSettings.txt

实验

我们首先确定 PLL1不稳定且未锁定的情况。 故障似乎与温度有关,因此我们从使用罐装空气冷却 IC 开始,尝试找出哪个 IC 敏感,阈值在哪里。 我们发现,当 LMK04828的封装温度高于36°C 且 LMK 已通电时,PLL1不会锁定。 使用热板和小型热风枪重复此测试、以加热 IC。 有趣的是、如果 LMK 在冷态时通电、它会立即锁定、并保持锁定状态远高于36°C

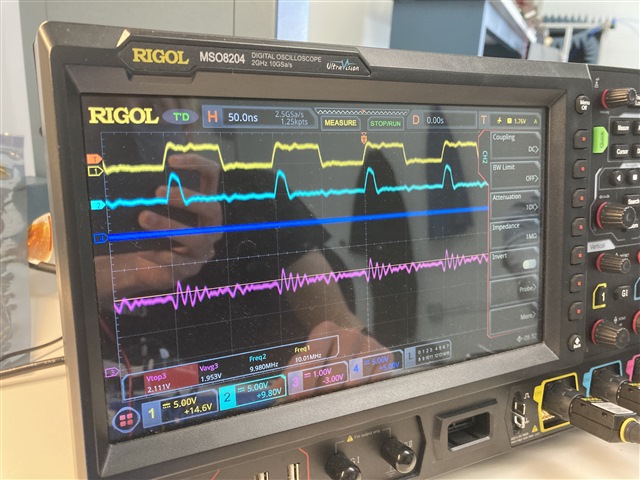

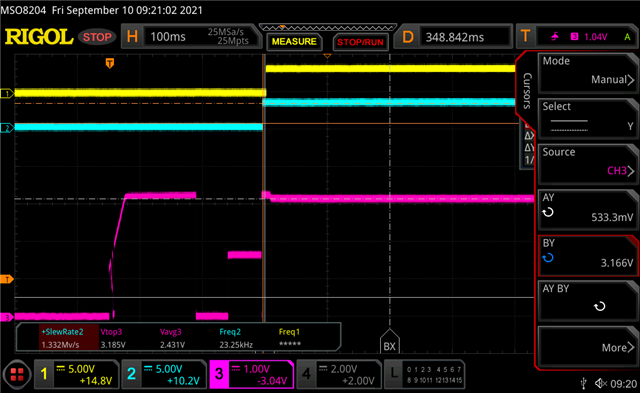

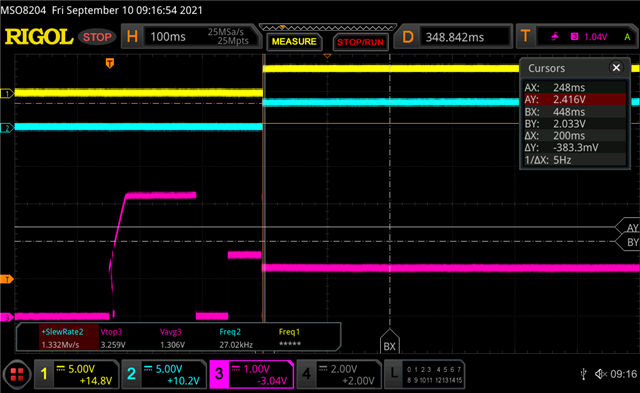

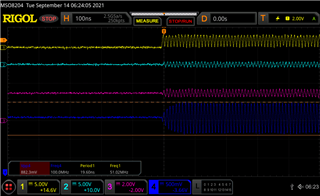

当 LMK 无法锁定时、分配给 PLL1_DLD 锁定状态的 Status_LD1 I/O 会在100MHz、10MHz、5MHz 或100MHz 的其他整数除法下振荡。 当我们的 PLL1_WND_SIZE 设置为43ns 且 PLL1_DLD_CNT 设置为8192时、如果数据表正确、我们不认为 LD1 PLL1锁定输出应能够在这些频率附近的任何位置切换状态。 我们担心 LMK 会进入未定义状态或反馈环路、对此我们没有明确的解决方案。 应该注意的是,在这种状态下,LMK 的数字输出和输入(SPI 和 LD1/LD2)在故障条件下在同一频率下存在明显的噪声。

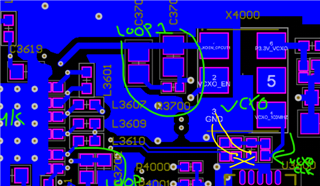

我们已经检查了 LMK 的3V3电源,它是干净的,并由一个本地低噪声 LDO (TPS7A4701)提供。 LMK 上各种电源进入 VCC 引脚的滤波通过适当的电容器去耦、并通过适当的低串联电阻铁氧体进行滤波。 根据我们的知识、去耦方案符合数据表中的建议。 我们还尝试使用与 LMK 电源不同的电源为 VCXO 供电,发现存在相同的行为。

我们的基准 OCXO (±50ppb)由另一个独立的 LDO 电源供电、并符合压摆率和电压要求。 我们的 VCXO (±50ppm 绝对牵引范围)还符合压摆和输出电压要求。 它的最大牵引范围为50ppm、在正常运行时的热漂移不超过18ppm (通过对热和冷 PLL1控制电压以及 ppm/V 值进行差分计算得出)。

我们已经针对带宽、100Hz、1000Hz 和20kHz 尝试了多个环路滤波器 R C 配置(原理图显示了100Hz 的环路滤波器 PLL1)。 全部使用 PLLatinum Sim 进行计算。 当 PLL 设法锁定时、PLL 的响应看起来会适当衰减、这使我们相信我们的环路滤波器已经过适当调优。

我们禁用了 RESET 输入、试图消除其响应噪声和复位 LMK 的可能性。 我们禁用了保持、禁用了 PLL 延迟、并且未启用同步或时钟源切换。 我们尝试通过更改分频器将 PLL1的检测频率从10MHz 降低到1MHz,并发现了相同的故障。 我们还尝试关闭整个 DCLK/SDCLK 输出级并发现相同的故障。

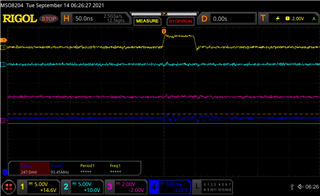

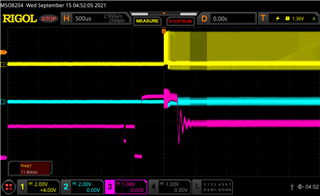

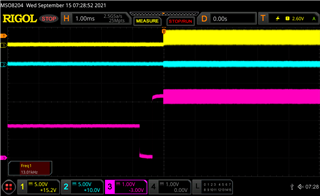

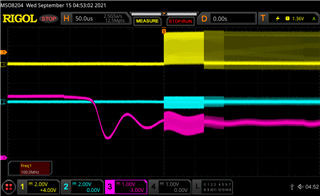

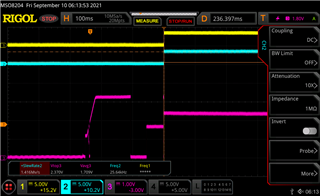

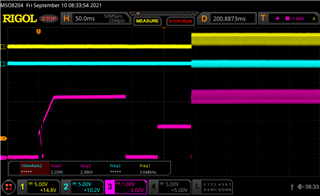

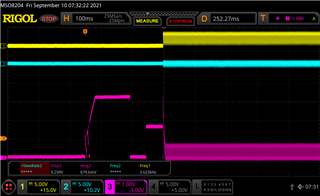

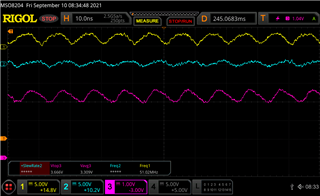

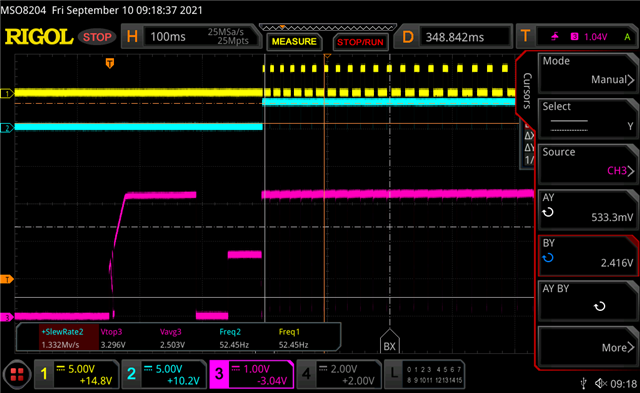

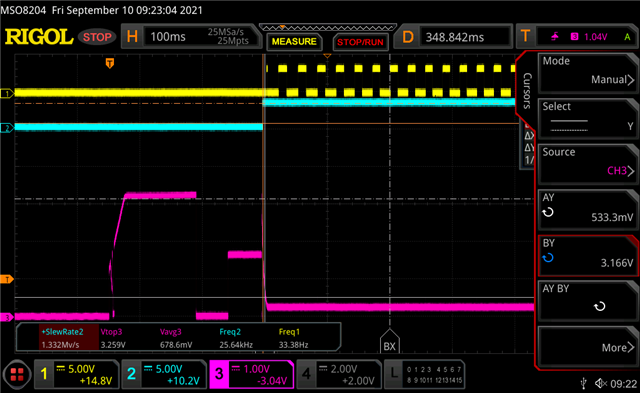

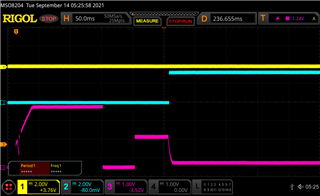

对于所有范围捕获:

迹线1 - LD1 (PLL1锁定)

迹线2 - LD2 (PLL2锁定)

迹线3 - PLL1控制电压输出

使用室温板成功锁定的捕获(RigolDS0.png)

锁定失败(控制电压漂移高达3V3)(RigolDS18.png)

锁定失败(控制电压降至接近0V)(RigolDS7.png)

锁定失败(更精细的时间刻度)(RigolDS20.png)

。

。