请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX2571 主题中讨论的其他器件: LMX2572

你(们)好。

我们知道 LMX2571中存在溢出问题。 我们修改了 CHDIV1、CHDIV2、乘法器和预分频器、以避免该问题。 但 我们无法避免的频率很少。 有什么建议吗?

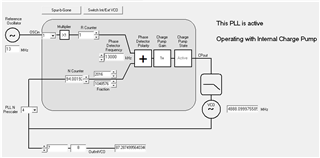

我们使用内部 VCO、设置如下所示、

输出频率:87.2875MHz

参考振荡器:13MHz (在我们的设计中是固定的)

OSCin:1.

乘法器:1.

R 计数器:1.

DEN:2^20

预分频器:4

CHDIV1:7

CHDIV2:8

我们需要的频率偏差为3.6KHz。

N 计数器的小数部分为2016。 FSK SPI 快速模式下满足3.6KHz 偏差的频率阶跃为4065。 则会发生溢出问题。

我们不想使用频率偏移来解决这个问题、因为接收器使用的频率是相同的。 如果我们在发送器中添加频率偏移、接收器将不会接收信号。

谢谢、

Ward