大家好、

我们使用 LMX594安排了一款产品。

当从 VCO/4更改为 VCO/8时、20LOG (2)不会降低6dB。

请给我建议以改进。

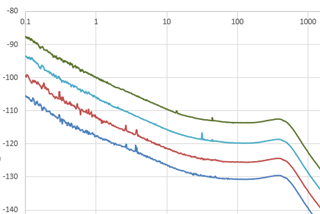

1kHz、 10kHz、 100kHz、 1MHz 偏移

Fout=VCO/2 (5500MHz):-102.2、-111.8、-113.4、-123.8 dBc/Hz

Fout=VCO/4 (2750MHz):-109.9、-118.3、-119.3、-129.6dBc/Hz

Fout=VCO/8 (1375MHz):-113.4、-122.4、-124.1、-134.1 dBc/Hz

Fout=VCO/16 (687.5MHz):-118.9 -128.1、-131.2、-141.2 dBc/Hz