您好、先生、

在我们的设计中、我们使用 LMK04828 CLK 合成器为 RFSoC 中的 RF-ADC 和 RF-DAC 提供时钟。 具有 SYSREF 作为反馈并具有嵌套双环回的单路 LMK 器件。

LMK 输入:

TCXO:10MHz LVCMOS (CLKIN 0)

VCXO:100MHz LVPECL

LMK 输出:

LVDS 输出

DCLKOUT:150MHz

SDCLKOUT:3.125MHz

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、先生、

在我们的设计中、我们使用 LMK04828 CLK 合成器为 RFSoC 中的 RF-ADC 和 RF-DAC 提供时钟。 具有 SYSREF 作为反馈并具有嵌套双环回的单路 LMK 器件。

LMK 输入:

TCXO:10MHz LVCMOS (CLKIN 0)

VCXO:100MHz LVPECL

LMK 输出:

LVDS 输出

DCLKOUT:150MHz

SDCLKOUT:3.125MHz

Harika、您好!

嵌套双环回配置在每个输出信号的输入基准之间建立了固定的确定性相位关系。 随附的应用手册解释了保持0延迟模式的标准。

https://www.ti.com/lit/an/snaa294/snaa294.pdf

如果您在基准时钟和所有输出时钟(包括 SYSREF )之间有确定性相位要求、则需要重新查看您的基准输入频率(10MHz)。

您的原理图看起来不错、建议遵循 LMK04828EVM 原理图、以保持正确的连接和正确的组件值、如 C11和 C16至10nF。

https://www.ti.com/lit/ug/snau145b/snau145b.pdf

对于 LVDS 输出、将560 Ω 电阻器放置在 ZU_PL_CLK_P/N、 ZU_SYSREF_P/N 和 ZU_PL_SYSREF_P/N 输出上。

此致、

Ajeet Pal

您好、Ajeet、

感谢你的答复。

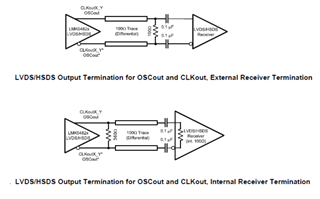

LMK04828数据表中提到了 LVDS 输出的两种终端方案、一种是具有外部接收器终端的 RX 器件、另一种是具有内部接收器终端的 RX 器件。

对于这些使用外部接收器终端的 LVDS 输出、ZU_PL_CLK_P/N、ZU_SYSREF_P/N 和 ZU_PL_SYSREF_P/N。

无论图中的上述配置如何、是否需要在两种配置的 LMK 输出端放置560 Ω?