您好!

我一直在使用 LMK04610时遇到问题。

我在 LMK04610评估板和特定板上都使用 LMK04610。

其目的是配置一些输出以生成特定的时钟频率(例如:104MHz),同时绕过两个 PLL 以保持相位噪声尽可能低,但我们也希望能够在 SPI 编程时生成 SYSREF 脉冲。 由于 SYSREF_REQ 也由 PLL 时钟计时、因此不能使用旁路模式(时钟分配模式)。

因此、我们选择将 LMK04610器件配置为单环路 PLL2运行模式(ref = CLKINx、振荡器=PLL2_OUTPUT)、同时还将 PLL2_CLKIN 启用为 OUTCHX。

我们使用 TICS PRO 软件在 LMK04610评估板上测试了此配置、设置如下:

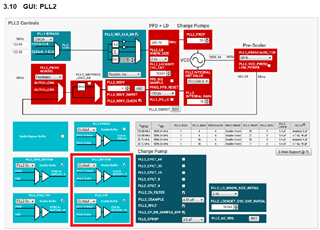

•PLL2设置

o CLKin0 = 624MHz、

o PLL2_RDIV = 6

o PLL2 PD = 104MHz < 250MHz

o PLL2 OSC = 5928Mhz (VCO 频率范围:5870MHz 至6175MHz)

o PLL2_预 分频器= 3

o PLL2_NDIV = 19

o PLL2 CLKOUT0=CLKOUT1=5928/6= 1976MHz

•通道/输出

CLK 输出

o 16位通道分频器= 6=> 624/6 = 104MHz

o CHX_SYSREF_REQ/SYSREF_EN=0、SYNC_EN=1

SYSREF 输出

o 16位通道分频器= 12=>624-12=52MHz

o SYSREF 脉冲计数器= 1、CHX_SYSREF_REQ/SYSREF_EN=1、SYNC_EN=1

o PLL2_REF_DIGCLK_DIV = 32,

o PLL2 PD =104MHz/32=3.25Mhz <«sysref 输出频率:52MHz»

问题是 PLL2未锁定。 如另一个主题中所建议的那样:“请注意,在分配模式下,不可能触发 SYSREF 脉冲,除非 PLL2预分频器的输出上有时钟,这意味着需要锁定 PLL2 (无论是否使用 PLL2)。” 不过、我们似乎看到了令人满意的结果。

您对此配置有何看法? 即使 PLL2未正确锁定、我们是否也可以使用此设置?

我们在特定电路板上测试了相同的设置、获得了相同的结果、但在生成1个 SYref 脉冲后、GLOBAL_SYSREF 位卡在1。

根据数据表、GLOBAL_SYSREF 位在满足 SYSREF 请求(自清零位)后自动清零。 当我们尝试将 global_SYSREF 重写为0时、它也不起作用。

全局 sysref 为1时、我们无法再触发 sysref 脉冲。 评估板不会出现此问题。

这是一个寄存器编程副本。

请您向我们提供一些支持、并告诉我们缺少什么?

此致、

Philippe

e2e.ti.com/.../conf_5F00_624MHz.txt