Other Parts Discussed in Thread: LMK04828, LMK04832, LMK00301

主题中讨论的其他器件: LMK04832、 LMK00301

你好

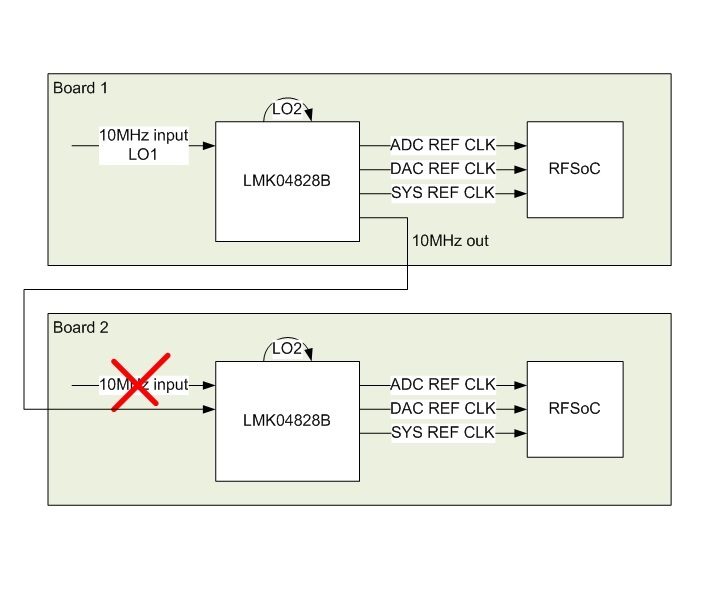

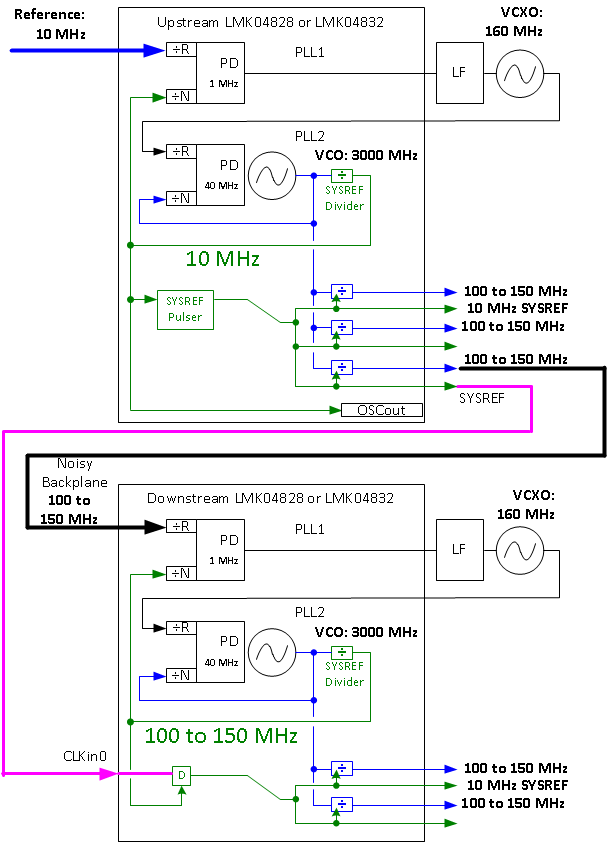

我的系统包含多个具有高速 ADC 和 DAC (基于 Xilinx RFSoC)的电路板、对于每个电路板、ADC 的时钟输入和 DAC 的参考时钟由 LMK04828器件生成。

由于 LMK04828器件需要双输入晶振和本地振荡器

我想问一下,我是否有办法使用多个 LMK0482B 在电路板 DAC/ADC 参考时钟之间同步

请参见图示

我的问题是两个板之间的 LO2不同

是否有办法做到这一点?

BR