主题中讨论的其他器件: CDCLVP1204

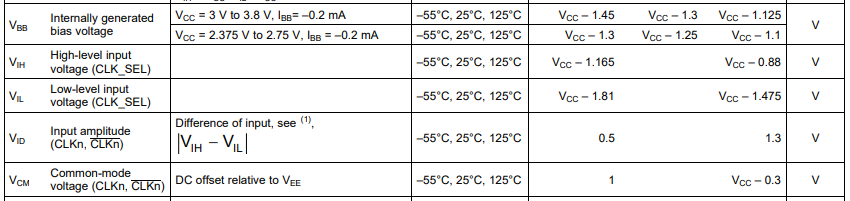

使用具有3.3V LVCMOS 单端输入的 CDCLVP111-SP 时钟缓冲器、遵循数据表图8中所述的接口。 它工作正常、但有一个问题、即对于 Vcc = 3.3V、VEE = 0V、尤其是 VID、时钟输入信号电平不符合第6.6节中列出的技术规格要求。

此外、不确定 VIH/VIL 规格是指什么、因为它们指出 CLK_SEL 应该与 LVTTL/LVCMOS 兼容。 例如、当 Vcc = 3.3V 时、VIH 限值最小为2.135V、最大为2.42V 这是否意味着 CLK_SEL 电平需要介于这些值之间、或者这是阈值电压的最小值和最大值?

这是否意味着时钟需要衰减? 我注意到一些 CDCLVP 时钟缓冲器(如 CDCLVP1204)具有单独的 LCMOS 输入规格作为单端输入。

在此应用中、输入频率为60MHz