主题中讨论的其他器件: LMX2594

大家好、

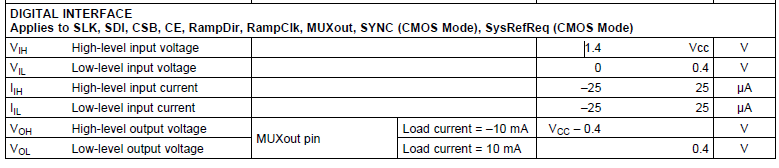

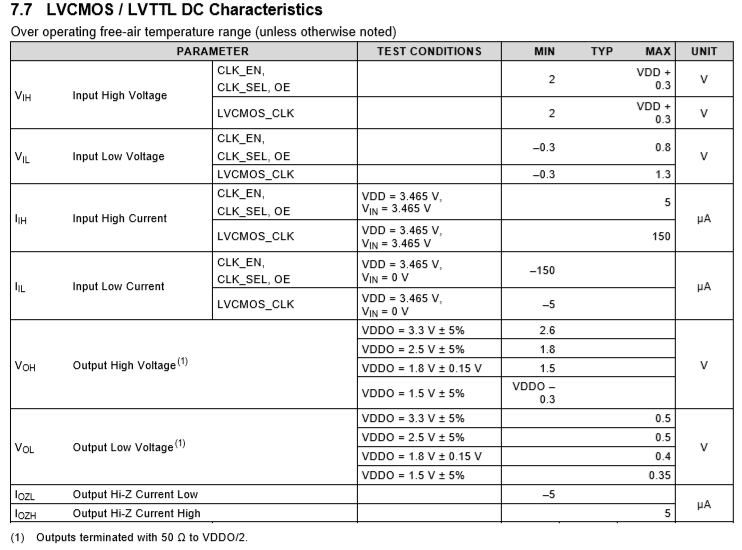

我们将 LMK00804BPW 用作其他3个 LMX2594RHAR 的同步器。 LMK 的 Q 输出直接连接到 LMX 的 SYNC 输入、而无需在线路上使用任何串联电阻器或上拉电阻器。 数据表中的 LMK Ω 说明:"端接50 μ A 的输出到 VDDO/2。" 这是否意味着需要在外部连接50欧姆的上拉电阻? 请详细说明此说明吗?

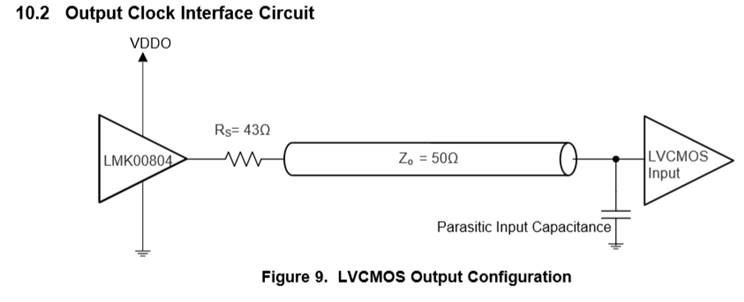

此外、在 LMK 的 EVM 中、输出端串联了一个43欧姆电阻。 是否包含在设计中、以及它如何与上面注释中提到的50 Ω 上拉电阻相关联。

谢谢、

苏丹。