主题中讨论的其他器件: ADC12DL3200

尊敬的 Sirs:

在我的设计中、我使用了四个 ADC12DL3200s。 ADC 时钟由以下链生成:

来源:LMX2594;

-缓冲器1:4 HMC987;

-开关 NB7V72MMNG (每个 ADC12DL3200一个);

- DIT2 NB7L32M 输出连接到 ADC12DL3200时钟输入。

开关 NB7V72MMNG 可选择内部时钟源(LMX2594+HMC987)

或外部时钟。

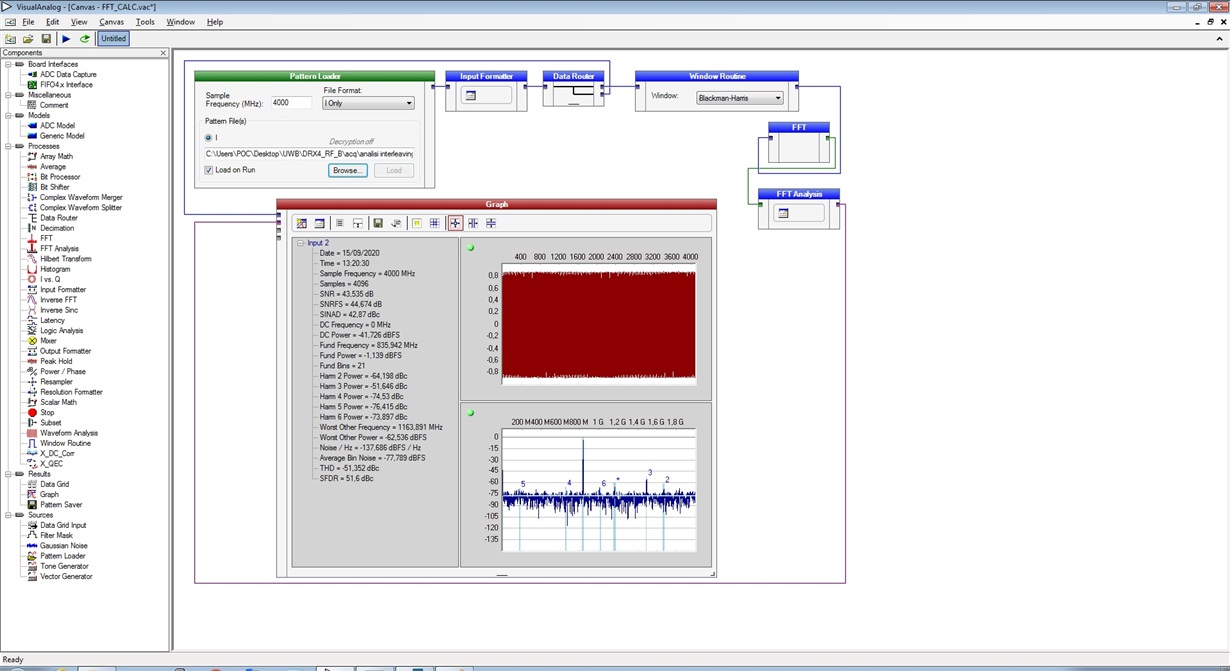

在此配置中、当我生成4GHz 时钟、然后使用 NNB7V72MMNG 进行选择时

内部源 ADC12DL3200工作正常、但也会产生 交错杂散

(时钟或增益)。 通常、此杂散具有-45dBFS 和-60dBFS 之间的功率。

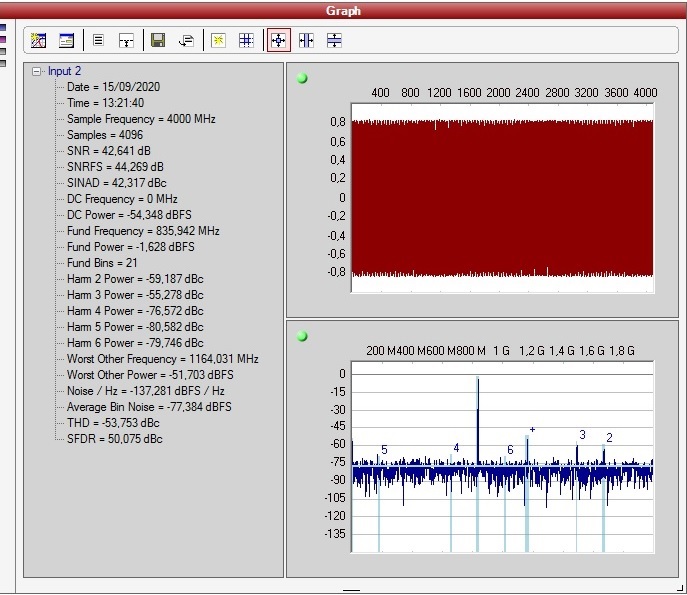

当我使用 NB7V72MMNG 选择由射频仪器生成的外部源时

(始终为4GHz)、那里的交错杂散信号

如果我重新校准 PLL、这种交错杂散会将值-45更改为-60dBFS (同样

如果我重新为电路板加电)、而当我重新校准 ADC 时、寄生功率是相同的。

这种伪波的可能来源之一是 PLL LMX2594和之间的互连

和 HMC987。 这两个组件具有交流耦合、LMX2594具有50 Ω 至3.3 Ω 的电阻

而 HMC987输入具有内部端接:PECL 端接和50 Ω。

您对交错伪波的来源有什么建议吗?

您能否帮助我了解 ADC12DL3200为何会产生交错杂散?

是否存在具有这些类型杂散的特定条件(例如、时钟不对称

或占空比不是50%)

您认为 LMX2594与 HMC987配合工作是否正常?

提前感谢。

此致。