Other Parts Discussed in Thread: LMK00304, LMK1D1204P

主题中讨论的其他器件:LMK00304、 LMK1D1204P、

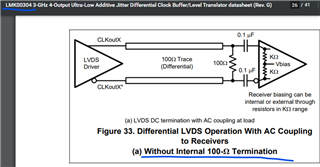

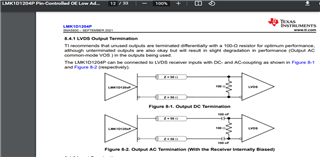

过去曾讨论过端接电阻器相对于 LVDS 交流耦合的放置位置。

下面的链接讨论了端接电阻器的位置。

假设 LVDS 接收器内部存在弱偏置、如果两个 A/B 结构的输入端都有时钟、则没有差异。

如果时钟未输入到输入引脚、则的结构可能会破坏和

B 的结构说明它具有保持特定状态而不抖动的优势。

但是、TI 通常会建议 B 结构。

但是、实际上、数据表中通过混合各种 A/B 结构提供了应用示例。

这使得它在实际应用中非常混乱。

下面的链接和数据表是一些让您感到困惑的示例。

e2e.ti.com/.../lmk00308-lvds-outputs-with-ac-coupling-to-receiver-with-internal-100-ohm-termination

LMK00304

LMK1D1204P

因此、我再次询问下面的 LVDS 交流耦合、希望它得到解决。

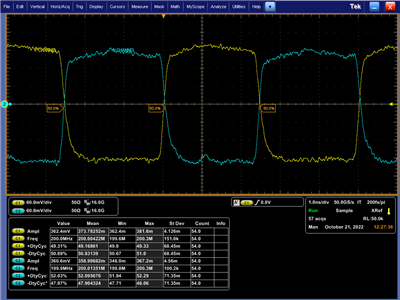

如果接收者的意见有一个固定的时钟,我个人认为 A 结构是好的。

原因是占空比变化。

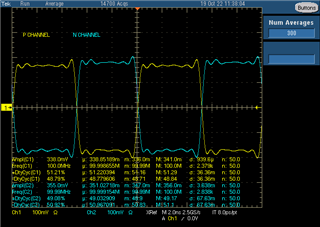

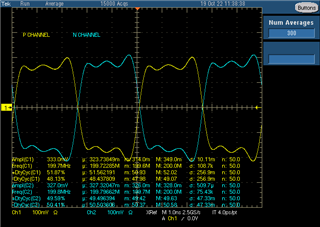

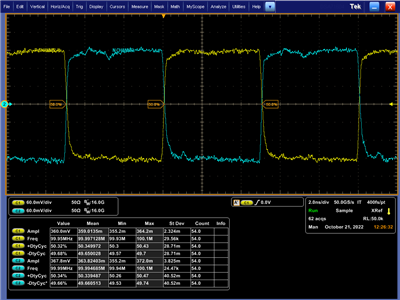

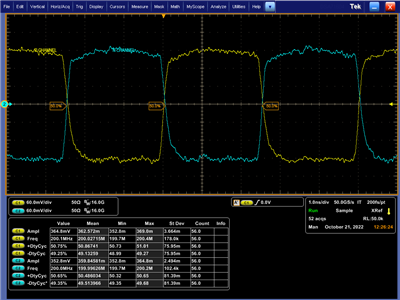

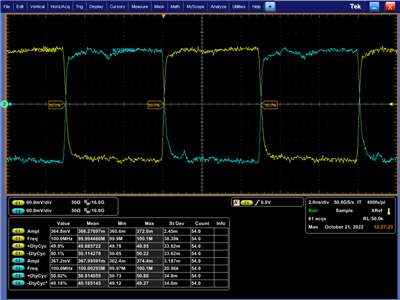

TI 说根据 A/B 结构没有占空比变化,但是这个答案适用于时钟的上升/下降时间非常短或者频率很低(f<100MHz)的情况。

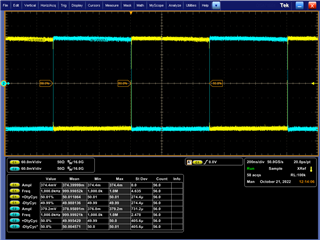

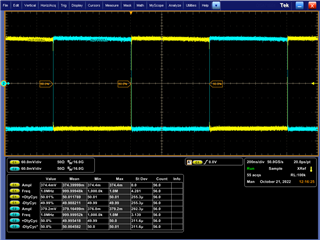

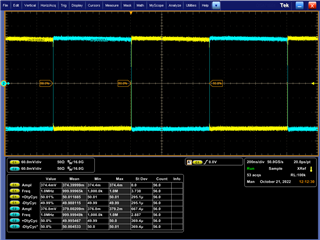

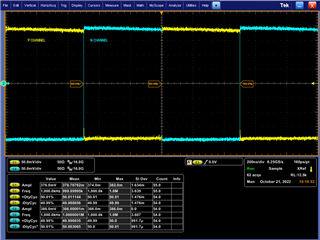

实际上、考虑到输入信号的上升/下降时间、我们认为占空比变化是随着频率的增加而发生的。

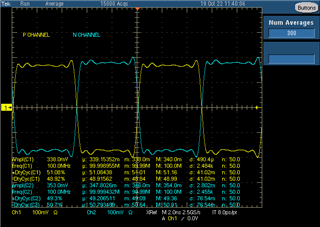

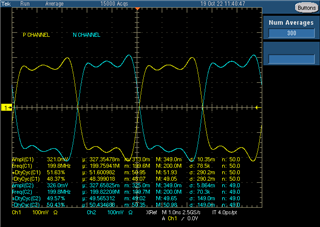

也就是说、低于100MHz (大约占空比= 50%)时、占空比变化很难看到、但在200MHz 时、占空比变化可见。

其原因是为了防止抖动、P/N 的偏移设置不同。

因此、如果使用 A 结构、则会忽略为防止抖动而应用的其他 P/N 偏移、并且信号的 P/N 偏移约等于1.2V、因此即使对于200MHz 信号、占空比变化也不会发生。

在 LVDS 交流耦合的情况下、如果时钟继续存在于接收器输入端、那么上述 A/B 结构中是否存在特别有问题的任何结构?

结构 B 是否仍然良好?

我还希望为时钟缓冲器提供 PSpice 模型。

此致

Lee HG