主题中讨论的其他器件:ADC12DJ3200、 LMK04828、 LMK04832、 LMK04808

问题、

如果布线长度匹配、那么两对器件和 SYSREF 时钟进入 FPGA JESD 块和 ADC12DJ3200的正确延迟是多少?

ADC 开发时钟的运行频率为3GHz、FPGA 开发时钟的运行频率为300MHz、SYSREF 时钟的运行频率为18.75MHz。

编辑:

很抱歉、这是针对 LMK04828的

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

问题、

如果布线长度匹配、那么两对器件和 SYSREF 时钟进入 FPGA JESD 块和 ADC12DJ3200的正确延迟是多少?

ADC 开发时钟的运行频率为3GHz、FPGA 开发时钟的运行频率为300MHz、SYSREF 时钟的运行频率为18.75MHz。

编辑:

很抱歉、这是针对 LMK04828的

您好!

如果您的系统只有1个 ADC12DJ3200和1个 FPGA、则2对 JESD204B 时钟(DEV CLK 和 SYSREF)不需要具有长度匹配、但每个器件的 DEV CLK 和 SYSREF 应具有长度匹配。

而如果您有多器件同步(多个 ADC)方案、则 JESD204B 时钟对应通过同步功能同步、并应具有与 ADC 匹配的长度迹线。

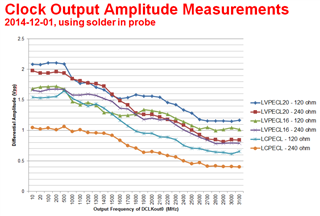

关于3GHz 的 ADC 时钟频率、LMK04828支持 LVDS/HSDS/LVPECL/LCPECL 输出、在较高频率下幅值较低。 下面是 FYR 频率下的 LVPECL/LCPECL 输出图。 对 ADC 所需的时钟振幅进行分析并选择输出格式。

然而、有一个 LMK04832 (与 LMK04828引脚兼容)、此器件支持 CML 输出并在较高频率下具有更高的振幅。

谢谢!

此致、

Ajeet Pal

您好!

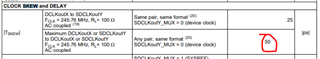

关于 DCLK 和 SYSREF 时钟的实际延迟设置、取决于分频值以及接收器端所需的设置和保持时序 DCLK 到 SDCLK 的偏差范围为|50ps|、根据 ADC 的设置和保持时序要求、需要优化延迟。

因此、在开始时、您可以为两者保留相同的延迟值、如果需要、您可能需要调整 DCLK 或 SDCLK 的值。 您可以按照 LMK04828数据表中的第9.3.4节了解 SYSREF 到器件时钟对齐练习。

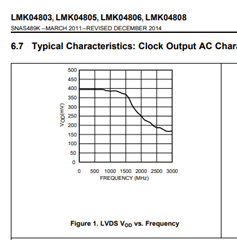

LVDS 格式的差分振幅在比 LVPECL/LCPECL 更高的频率下显著降低。

LMK04808具有与 LMK04828类似的输出缓冲器。

谢谢!

此致、

Ajeet Pal