主题中讨论的其他器件:TPL5111、 TPS63050

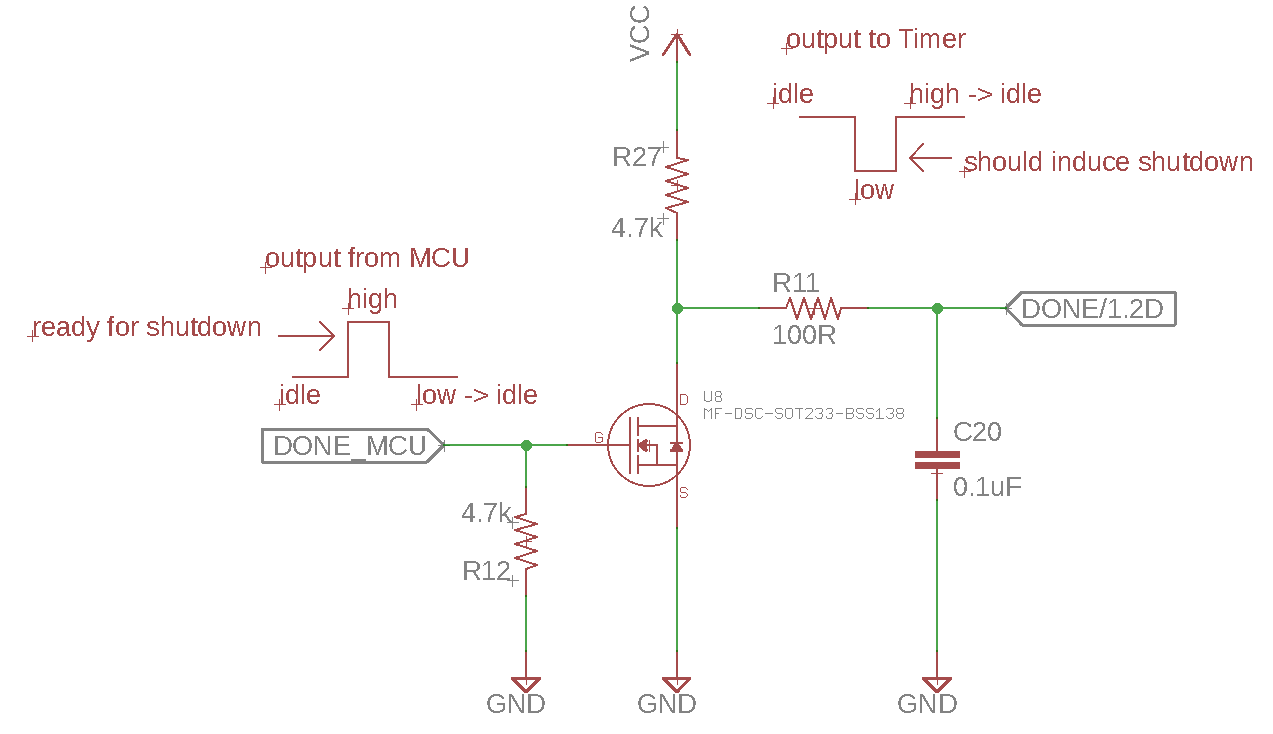

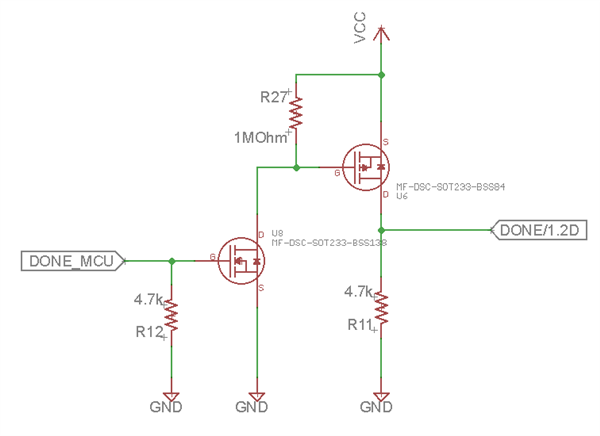

在我看来、将 DONE 信号从高电平状态而不是低电平状态变为高电平状态可能是一种更稳健、更简单的方法(与我在 TPL5111应用手册中看到的方法相比)。 我设计了下面的胶合逻辑电路来实现这一结果。 使用此电路、微控制器必须将其"完成"输出驱动为高电平、然后驱动为低电平、以请求计时器关断。

我在这里的想法是、此拓扑在系统上电期间不会受到干扰的影响(进一步被输出级上的无源低通滤波器抑制。 该电路还用于将电池电压域(下面原理图中的 VCC)与 MCU 信号所在的系统电源域隔离。

希望 TI 的某个人可以查看此设计决策、并考虑此方法是否有任何重大不利之处?