我们正在使用 TX 上的 LMX2571开发 DMR 基站。

PLL 校准会产生许多频率、从而产生不可预测的行为。

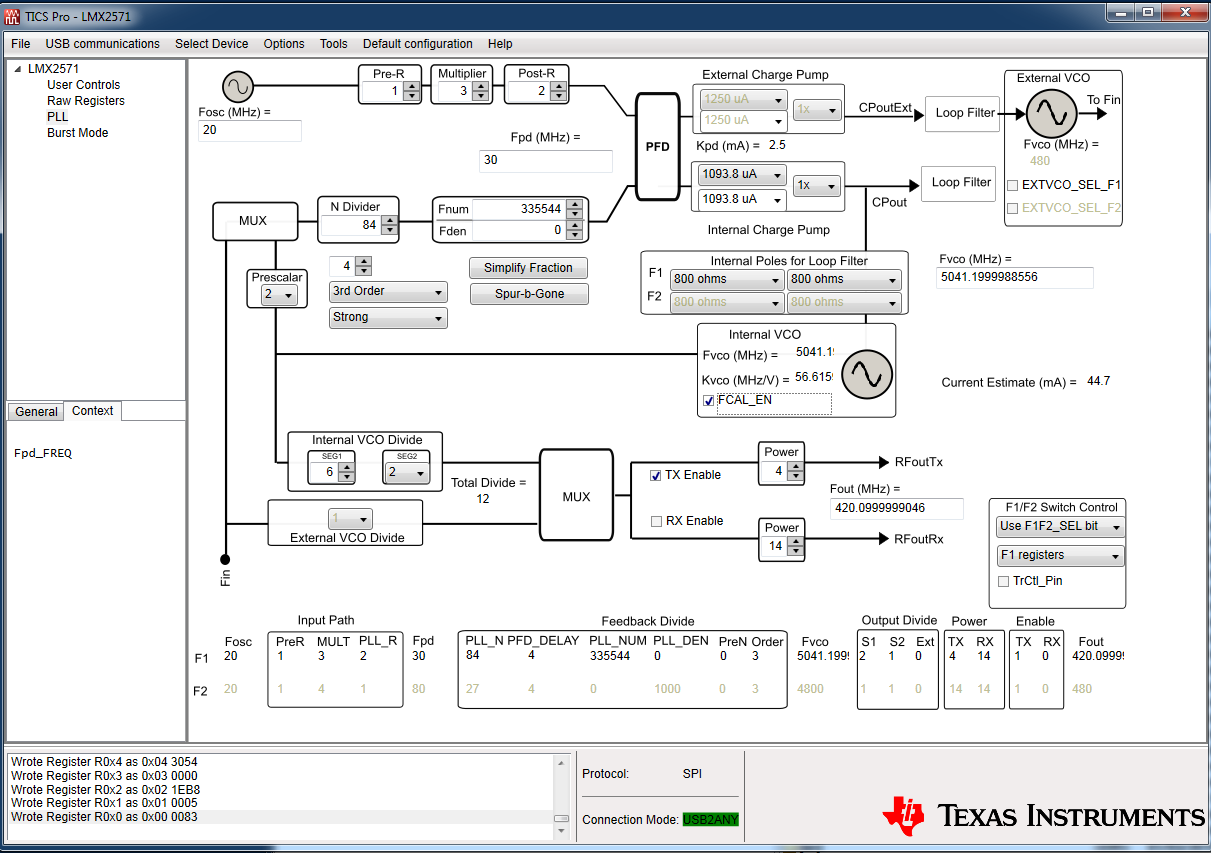

校准显然可以进入两种状态。 下图显示了相关事实:通过写入 FCAL_EN 进行的每次新校准都会导致-47dBc 的杂散或-49dBc 的杂散(变化为50:50)。 所有其它寄存器保持不变! 在我们的基站中、我们发现两个校准状态之间的差异超过10dB。

这些校准之间有何差异? 是否有可能确定这两个国家中的哪一个已被采用,以及如何强制建立更好的国家?

这些屏幕截图是在421.1 MHz 下使用 LMX2571EVM 拍摄的、使用 TICS Pro 和以下寄存器进行编程:

R60 0x3CA000

R58 0x3A8C00

R53 0x357806

R47 0x2F6000

R46 0x2E001A

R42 0x2A0210

R41 0x290807

R40 0x28071C

R39 0x2711FB

R35 0x230C83

R34 0x221000

R33 0x210000

R32 0x200000

R31 0x1F0000

R30 0x1E0000

R29 0x1D0000

R28 0x1C0000

R27 0x1B0000

R26 0x1A0000

R25 0x190000

R24 0x18000E

R23 0x170E84

R22 0x168584

R21 0x150101

R20 0x14301B

R19 0x1303E8

R18 0x120000

R17 0x110000

R16 0x100000

R15 0x0F0000

R14 0x0E0000

R13 0x0D0000

R12 0x0C0000

R11 0x0B0000

R10 0x0A0000

R9 0x090000

R8 0x080004

R7 0x070E84

R6 0x068683

R5 0x050201

R4 0x043054

R3 0x030000

R2 0x021EB8

R1 0x010005

R0 0x000083

下面是一个来自基准频率为25MHz 的基站的示例、其中效应更频繁发生。