您好!

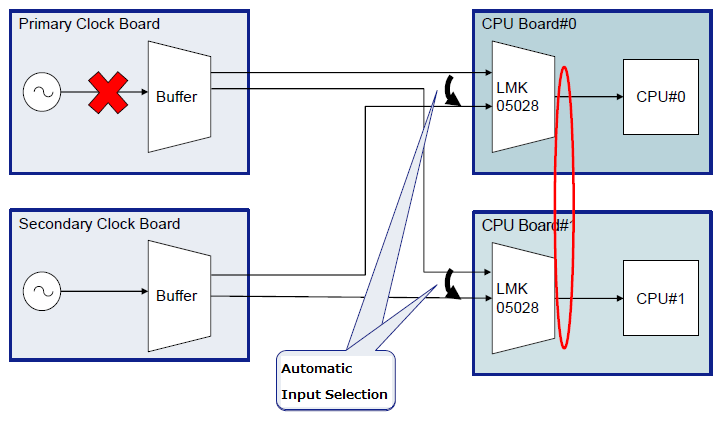

我的客户正在考虑使用以下配置。

・即使其中一个时钟源丢失、LMK05028也应通过自动输入选择切换到其中一个时钟源。

⇒可以切换。

•希望 CPU 在发生切换时同步运行。

⇒是否同步运行取决于客户系统的要求。

[第1季度]

上述用法是否假定为器件?

我认为上述用途是一种特殊用途。

[第2季度]

客户期望器件之间切换事件期间的输出频率相同。

他们的想法如下。

如果同一 PLL IC 的输入切换到同一参考时钟、PLL IC 的行为是相同的。

也就是说、输出波动是相同的。

我认为以下因素会导致 PLL 运行的变化。

・KPD

・Z (s)

・KVCO

・输入的初始状态

我认为 LMK05028是 DPLL、因此 KPD Z (s) KVCO 没有变化。

在这种情况下、我认为客户有理由。

但是、初始状态变化是一个外部因素、需要由客户进行评估。

没有描述切换时输出波动的规格。

我的理解是否正确?

如果您有任何疑问、请告诉我。

此致、

Kaede Kudo